# **Lowpass L Matching Network Designer**

#### **Table of Contents**

- I. General Impedance Matching

- II. Impedance Transformation for Power Amplifiers

- III. Inputs

- IV. Calculations

- V. Outputs

- VI. Functions

- VII. Examples

- VIII. Parameters

- IX. Impedance Matching with a Smith Chart

- X. S Parameters on a Smith Chart

- XI. Sensitivity Analysis

- XII. Amplitude Constrained Impedance Transformation

- XIII. Layout Notes for the Lowpass L Matching Network

- XIV. Copyright Information

- ▶ useful functions and identities

- **▶** Units

- **▶** Constants

#### Inputs

$Z_L := 200 \text{ohm} - \text{j} \cdot 50 \text{ohm}$  Load impedance

$Z_S := 50 \text{ohm} + \text{j} \cdot 25 \text{ohm}$  Source impedance

$f_{min} := 900MHz$  Lower edge of band frequency

$f_{\text{max}} = 900 \text{MHz}$  Upper edge of band frequency

#### **Calculations**

The L matching network is only designed to provide maximum power transfer at one frequency. In other words it is a narrow band matching network. Given a band of input frequencies, we set design the matching network for the center of the band.

$$f_{c} := \frac{f_{min} + f_{max}}{2} \qquad f_{c} = 900 \,\text{MHz}$$

$$f := f_{c} \qquad \omega_{c} := 2 \cdot \pi \cdot f_{c} \qquad \omega := 2 \cdot \pi \cdot f$$

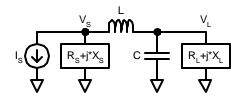

The first step in synthesizing an impedance matching network is to deimbedd the source and load reactances. Because the matching network consists of a inductor in series with the source, the source impedance is converted into an equivalent series resistance and inductance. The equivalent series inductance and resistance of source impedance are:

$$R_S := Re(Z_S)$$

$R_S = 50 \text{ ohm}$

$L_S := \frac{Im(Z_S)}{\omega}$   $L_S = 4.421 \text{ nH}$

Deimbedding the load reactance is a little more difficult, because the impedance is in parallel. The calculation is easy to perform by converting the input impedance to an admittance with a complex math processor, such as Mathcad, but is performed here assuming only a real processor is available. The equivalent parallel capacitance and resistance of load impedance are:

$$\begin{aligned} Q_L &\coloneqq -\frac{\text{Im}(Z_L)}{\text{Re}(Z_L)} & Q_L = 0.25 \\ R_L &\coloneqq \text{Re}(Z_L) \cdot \left(1 + {Q_L}^2\right) & R_L = 212.5 \text{ ohm} \\ C_L &\coloneqq \frac{Q_L}{\omega \cdot R_L} & C_L = 0.208 \text{ pF} \end{aligned}$$

With the source and load reactances deimbedded, we can synthesize the matching network using the real part of the source and the load. Our goal here is to size the L and the C such that source and the load sees the conjugate of it's impedance looking into the network. A matched network sliced anywhere in the network will have a conjugate impedance looking in either direction.

$$Z_{left} = \overline{Z_{right}}$$

The right side of the matching network consists of a parallel resistance and reactance. This can be expressed in a simplified form with the parallel resistance and the Q of the source.

$$Z_{\text{right}} = \frac{1}{\frac{1}{R_{\text{right}}} + \frac{1}{j \cdot L_{\text{right}}}} = \frac{1}{G_p + j \cdot B_{\text{right}}} = \frac{R_p}{\left(1 + j \cdot Q_{\text{right}}\right)}$$

The left side of the matching network consists of a series resistance and reactance. This can be expressed in a simplified form with the series resistance and the Q of the load.

$$\overline{Z_{\text{left}}} = R_{\text{left}} + \frac{1}{j \cdot C_{\text{left}}} = R_{\text{S}} + j \cdot X_{\text{left}} = R_{\text{S}} \cdot (1 - j \cdot Q_{\text{left}})$$

Because the left and right resistances must be equal, and the reactances conjugates of each other, the Q's of the left and right sides must be equal. Setting the left impedance and right conjugate equal to each other, and setting the O's equal gives the following equality.

$$\frac{R_p}{(1+j\cdot Q)} = R_S \cdot (1-j\cdot Q)$$

Solving this expression gives a general expression for the Q of matching network. Note the Q value is fixed by the source and load impedance for the L matching network. For higher order networks, and for equal source and load resistance, the Q of the network may be chosen.

$$Q := \sqrt{\frac{R_L}{R_S}} - 1$$

$Q = 1.803$

This Q will serve as a lower bound for pi and T matching networks, and as an upper bound for cascaded L matching networks. Note the difference between network Q and component Q. Network Q is usually on the order of zero to three, to reduce sensitivity of the network. Component Q is much higher, typically 10 to 100, to

Given the Q of the left and right half sides of the network, and the effective source and load impedances, we can find the matching network inductance and capacitance without source inductance deembedded

$$L_{T} := \frac{Q \cdot R_{S}}{\omega}$$

$$L_{T} = 15.94 \text{ nH}$$

$$C_{T} := \frac{Q}{\omega \cdot R_{L}}$$

$$C_{T} = 1.5 \text{ pF}$$

The final impedance network is found by substracting the source inductance from the matching inductance and the load capacitance from the matching capacitance.

$$L := L_T - L_S$$

$L = 11.519 \, \text{nH}$   $C := C_T - C_L$   $C = 1.292 \, \text{pF}$

As a check of the matching network, we calculate the input and output impedance of the network to see if they are the conjgate of the source and the load.

$$\begin{split} Z_i &\coloneqq j \cdot \omega \cdot L + Z_L \parallel \left(\frac{1}{j \cdot \omega \cdot C}\right) \\ Z_o &\coloneqq \left(Z_S + j \cdot \omega \cdot L\right) \parallel \left(\frac{1}{j \cdot \omega \cdot C}\right) \end{split} \qquad \qquad Z_i = 50 - 25i \text{ ohm} \qquad Z_S = 50 + 25i \Omega \\ Z_o &\coloneqq \left(Z_S + j \cdot \omega \cdot L\right) \parallel \left(\frac{1}{j \cdot \omega \cdot C}\right) \end{aligned} \qquad \qquad Z_o = 200 + 50i \text{ ohm} \qquad Z_L = 200 - 50i \Omega \end{split}$$

### **Outputs**

$C = 1.292 \, pF$  $L = 11.519 \, nH$  Load Capacitance (in parallel with load) Source Inductance (in series with source)

## **Copyright Information**

All software and other materials included in this document are protected by copyright, and are owned or controlled by Circuit Sage.

The routines are protected by copyright as a collective work and/or compilation, pursuant to federal copyright laws, international conventions, and other copyright laws. Any reproduction, modification, publication, transmission, transfer, sale, distribution, performance, display or exploitation of any of the routines, whether in whole or in part, without the express written permission of Circuit Sage is prohibited.