# Bandgap Voltage and Current Reference Designer

Note: This file is a reduced version (true, but hard to believe since this file is so big) of a more extended version. The reduction is still in progress, so please excuse the current errors.

Table of Contents

## **Table of Contents**

Introduction **Optional Inputs** Inputs Model File Cost of Area Cost of Power **Total Cost** Optimal Noise and Mismatch Budgeting Bandgap Notes from Paul Gray **Basic Bandgap Topology Bandgap Design Equations Bandgap Headroom Constraints BiCMOS** Bandgap Noise Analysis **Current Mirror Variance Bandgap Variance Derivation Output Resistance Derivation PSRR** Derivation **Start-Up Circuitry BiCMOS Bandgap Performance CMOS** Bandgap Noise Analysis of CMOS Bandgap Phase Margin and Compensation of CMOS Bandgap **CMOS** Bandgap Area **CMOS Bandgap Bias Sizing CMOS Bandgap Current Sizing** Sizing for Bandgap Variance **Device Sizing Performance Measures Outputs** Noise and Variance of Resistor Divider **Op-Amp Voltage-to-Current Converter with NMOS Follower** Op-Amp Voltage-to-Current Converter with NMOS Follower Bandgap Voltage-to-Current Converter Widlar CMOS Bandgap Reference

# Introduction

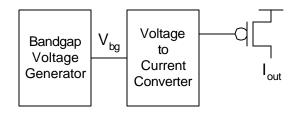

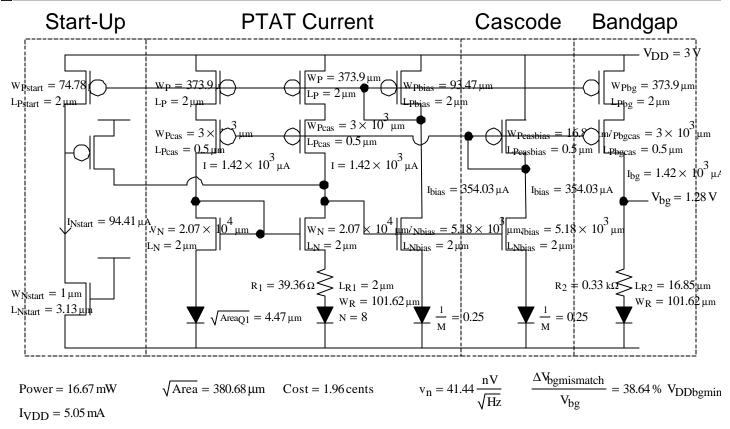

Fig. 0: Overall block diagram of bandgap current generator

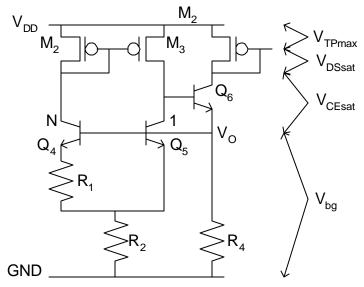

A general purpose bandgap voltage generator for BiCMOS technologies is shown in figure 1. Alternate versions of the reference exclude the emitter follower,  $Q_6$ , or replace with it with some form of operational amplifier. The emitter follower or operational amplifier circuitry do not contribute much low frequency noise or variance in the output voltage, while migitating second order effects, such as output resistance and base currents. These more advanced versions typically require more area and power, but are usually justified by their advantages. The following design and analysis routines apply the more advanced versions as well.

Fig. 1: Basic BiCMOS bandgap circuit with a) no beta-booster, b) emitter-follower beta-booster, and c) op-amp beta-booster.

Almost all reference circuits have multiple stable operating points and require additional start-up circuitry to insure the main circuit is the correct region of operation. The design and sizing of the start-up circuitry is described in a later section. Short channel effects are not added, because the lengths are usually made long for bandgap circuits to improve matching and reduce 1/f noise. The extra length hurts bandwidth, but bandgaps are primarily DC bias circuits, so BW doesn't matter as much.

#### Introduction

Units

Constants

Optional Inputs

Inputs

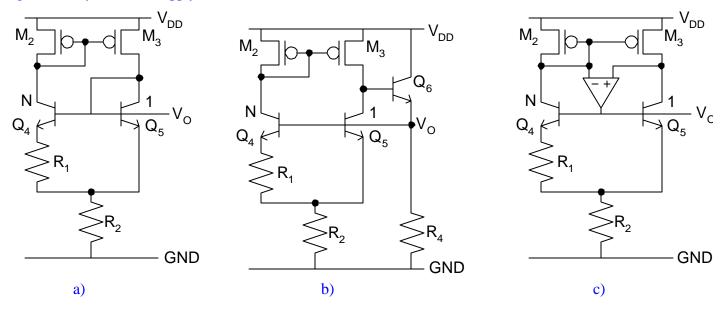

# Inputs

Bandgap Design and Analysis In this section you will enter the requirements for the bandgap, but keep in mind that bandgaps are inherently noisy

## General Bandgap Notes

Bandgap voltages are temperature independent voltages, created by adding the positive temperature coefficient of a thermal voltage to the negative temperature coefficient.

$V_0 = V_{BE} + K_{ptat} \cdot V_T = V_{bg}$

Bandgap Output Voltage

The thermal voltage can be expressed as a fixed voltage at the nominal temperature, Temp, rimes normalized temperature:

$V_{T} = \frac{k \cdot \text{Temp}}{q} \cdot \frac{T}{\text{Temp}} \qquad V_{T0} = \frac{k \cdot \text{Temp}}{q}$

The base-emitter voltage can be expressed in the following form. It initially appears to have a positive temperature coefficient, because of the VT term, but the temperature coefficient of Is will make the overall temperature coefficient of V<sub>BE</sub> negative.

$$V_{BE} = V_{T} \cdot \ln \left(\frac{I_{C}}{I_{S}}\right) = V_{T0} \cdot \frac{T}{\text{Temp}} \cdot \ln \left(\frac{I_{C}}{I_{S}}\right)$$

**Base Emitter Voltage**

The bias current for the base emitter junction current is usually generated with a PTAT voltage and a resistor. The overall temperature coefficient is found with a combination of the two temperature coefficients.

$$I_{C} = \frac{V_{T}}{R(T)} = I_{0} \left(\frac{T}{T_{0}}\right)^{\alpha}$$

for PTAT current biasing

(includes resistor temperature coefficient)

The resistor temperature coefficient is typically around 1000-2000ppm/C for well resistors and +/-300ppm/C for polysilicon resistors.

$$R(T) = R_0 \left[ 1 + RTC \left( T - T_0 \right) \right] \qquad RTC \coloneqq 2070 \frac{ppm}{degC} \qquad RTC \cdot Temp = 0.64$$

To solve for  $\alpha$ , we substitute can make use approximation  $(1 + x)^{\alpha} = 1 + \alpha \cdot x$  on R(T)

<sup>Ba</sup>

$$R_0 \left(\frac{T}{T_0}\right)^{\alpha_R} = R_0 \left(1 + \frac{T - T_0}{T_0}\right)^{\alpha_R} = R_0 \left(1 + \alpha_R \cdot \frac{T - T_0}{T_0}\right) = R_0 \left[1 + RTC \cdot (T - T_0)\right]$$

$\alpha_R = RTC \cdot T_0$

$I_C = \frac{V_{T0}}{R_0} \left(\frac{T}{T_0}\right)^{1 - \alpha_R} = I_{C0} \left(\frac{T}{T_0}\right)^{1 - RTC \cdot T_0}$

$\alpha := 1 - RTC \cdot Temp \quad \alpha = 0.36$

$I_S = \frac{q \cdot n_i^2 \cdot D_n \cdot A_{EB}}{Q_B}$

$D_i de Reverse Saturation Current$

$D_n = V_T \cdot \mu_N = V_{T0} \cdot \frac{T}{T_0} \cdot \mu_N$

$\mu_N = C \cdot T^{-n} = C \cdot T_0^{-n} \cdot \left(\frac{T}{T_0}\right)^{-n} n := 0.8$

$n_i^2 = D \cdot T^3 \cdot e^{-\frac{V_{G0}}{V_T}} = D \cdot T_0^3 \cdot \left(\frac{T}{T_0}\right)^3 \cdot e^{-\frac{V_{G0} \cdot T_0}{V_{T0} \cdot T}}$

Instrinsic Carrier Concentration as a funct

Temperature

Saturation Current

on Constant

y as a function of Temperature

Concentration as a function of

Making substitutions for  $n_i^2$ ,  $m_N$ ,  $D_n$ ,  $I_S$  and  $I_C$  into  $V_{BE}$  then simplifying yields:

$$V_{BE} = V_{G0} - V_{T} \cdot \left[ (4 - n - \alpha) \cdot \ln(T) - \ln \left[ \frac{Q_{B} \cdot I_{0} \cdot \left( \frac{1}{T_{0}} \right)^{\alpha}}{D \cdot k \cdot C \cdot A_{EB}} \right] \right] = V_{G0} - V_{T0} \cdot \frac{T}{T_{0}} \cdot \left[ (\gamma - \alpha) \cdot \ln \left( \frac{T}{T_{0}} \right) + \ln \left( \frac{I_{0} \cdot Q_{B}}{q \cdot D \cdot V_{T0} \cdot C \cdot T_{0}^{3-n} \cdot A_{EB}} \right) \right]$$

Making the following substitutions

$$EG = \frac{I_0 \cdot Q_B}{q \cdot D \cdot V_{T0} \cdot C \cdot T_0^{3-n} \cdot A_{EB}} \qquad \gamma := 4 - n$$

Yields the following results

$$V_{BE} = V_{G0} - V_T \cdot \left[ \left( \gamma - \alpha \right) \cdot \ln \left( \frac{T}{T_0} \right) - \ln(EG) \right]$$

Making substitution for  $V_{BE}$  into  $V_{o}$ .

$$V_{o} = K_{ptat} \cdot V_{T0} \cdot \frac{T}{T_{0}} + V_{G0} - V_{T0} \cdot \frac{T}{T_{0}} \cdot \left[ \left( \gamma - \alpha \right) \cdot \ln \left( \frac{T}{T_{0}} \right) - \ln(EG) \right]$$

Take the derivative of  $V_o$  with respect to temperature and set it equal to zero to solve for  $K_{ptat}$ :

$$\frac{d}{dT}V_{0} = 0 = K_{\text{ptat}} \cdot \frac{V_{\text{T0}}}{T_{0}} - \frac{V_{\text{T0}}}{T_{0}} \cdot \left[ (\gamma - \alpha) \cdot \ln\left(\frac{T}{T_{0}}\right) - \ln(\text{EG}) \right] - \frac{V_{\text{T0}}}{T_{0}} \cdot (\gamma - \alpha)$$

$$K_{\text{ptat}} = \left(1 + \ln\left(\frac{T}{T_{0}}\right)\right) \cdot (\gamma - \alpha) - \ln(\text{EG})$$

at  $T=T_0$ :

$K_{ptat} = \left( \gamma - \alpha \right) - \ln(\text{EG})$

Plugging  $K_{\text{ptat}}$  back into the equation for  $V_{\text{o}}$  yields:

$$V_{0}(T) := V_{G0} + \frac{k \cdot T}{q} \cdot (\gamma - \alpha) \cdot \left(1 + \ln\left(\frac{\text{Temp}}{T}\right)\right)$$

at T=T<sub>0</sub>:

a

$$v_{1} = v_{00} \pm \frac{k \cdot \text{Temp}}{k}$$

$(v_{1} = \alpha)$   $v_{2} = 1.2812 \text{ V}$  Bandgan voltage at center of temperature range

Ba 'bg - 'GU '

a

$\gamma_{\text{bg}} = 1.2012$  v Duriegup voringe in center of competitude range

Here we don't see dependence of the process variations on the bandgap voltage. This will be shown in the next section.

Bandgap voltage at low end of temperature range

$$\Delta V_{start} := \frac{k \cdot Temp}{q} \cdot (\gamma - \alpha) \cdot \left[ 1 - \frac{Temp \min}{Temp} \left( 1 + ln \left( \frac{Temp}{Temp \min} \right) \right) \right]_{tart} = 1.95 \text{ mV} \text{ tror voltage at low end of temperature range}} \\

V_0(Temp max) = 1.2795 V Bandgap voltage at the high end of the temperature range

$$\Delta V_{stop} := \frac{k \cdot Temp}{q} \cdot (\gamma - \alpha) \cdot \left[ 1 - \frac{Temp \max}{Temp} \left( 1 + ln \left( \frac{Temp}{Temp \max} \right) \right) \right]_{lop} = 1.68 \text{ mV} \text{ fror voltage at high end of temperature range}} \\

\Delta V_{max} := max \left( \Delta V_{start} \Delta V_{stop} \right) \right) \qquad \Delta V_{max} = 1.95 \text{ mV} \\

V_{ave} := min((V_0(Temp \max) V_0(Temp \min))) + \frac{\Delta V_{max}}{2} V_{ave} = 1.28 \text{ V} \\

\frac{\Delta V_{max}}{V_{ave}} = 0.15\% \qquad \frac{\Delta V_{max}}{V_{ave}} = 1.52 \times 10^3 \text{ pm} \qquad \frac{\Delta V_{max}}{V_{ave} \text{ temp}} = 4.9 \frac{\text{ ppm}}{\text{ degC}} \\

\text{ i = 0. (num - 1) Index Vector for Plotting} \\

\text{TempK}_i := \frac{1}{num - 1} \cdot (\text{Temp max} - \text{Temp min}) + \text{TempminFemperature vector for Plotting} \\

0 \text{ tupt Voltage as A Function of Temp} \\

\frac{0}{1.280} \frac{1.2805}{1.2805} \frac{1.2805}{1.2790} \frac{1.280}{0.20} \frac{1.280}{0.20}$$$$

#### **Questions and Answers:**

Q: What type of resistor should be used to minimize the temperature coefficient of the bandgap voltage? A: The answer depends on whether the device will be trimmed or not. If it is trimmed than the answer can easily be seen from the equations for DV. If you can make g-a=0, then the bandgap will exhibit no temperature dependence. If you make the substitution for a the equation for DV becomes:

$$\Delta \mathbf{V} = \frac{\mathbf{k} \cdot \mathbf{T}_0}{q} \cdot \left(\gamma - 1 + \text{RTC} \cdot \mathbf{T}_0\right) \cdot \left[1 - \frac{\mathbf{T}_{\text{start}}}{\mathbf{T}_0} \cdot \left(1 + \ln\left(\frac{\mathbf{T}_0}{\mathbf{T}_{\text{start}}}\right)\right)\right]$$

No process variations

Solving for RTCC, when  $\Delta V$  is set to zero equals:

$$RTC_{opt} := \frac{1 - \gamma}{Temp}$$

$RTC_{opt} = -7.09 \times 10^3 \frac{ppm}{K}$

A negative resistive temperature coefficient of this magnitude is usually not available, so it could be best to use

# Bandgap Design and Analysis the most negative temperature coefficient.

| Here are some example temperature coefficients from a 0.5um BiCMOS process |  |  |  |  |

|----------------------------------------------------------------------------|--|--|--|--|

| Temperature Coefficient of NP Polysilicon Resistor                         |  |  |  |  |

| Temperature Coefficient of PC Polysilicon Resistor                         |  |  |  |  |

| Temperature Coefficient of N+ Reach-Through Resistor (diffusion)           |  |  |  |  |

| Temperature Coefficient of NPN Base Resistor (diffusion)                   |  |  |  |  |

| Temperature Coefficient of NPN Extrinsic Base Resistor (diffusion)         |  |  |  |  |

| e temperature coefficients from a 0.5um SiGe BiCMOS process                |  |  |  |  |

| Temperature Coefficient of Ion Implant Resistor                            |  |  |  |  |

| Temperature Coefficient of Polysilicon Resistor                            |  |  |  |  |

|                                                                            |  |  |  |  |

Even though the polysilicon resistors will result in a smaller temperature coefficient, the difference between the best and worst ideal temperature coefficients is only 0.7mV, or a 33% reduction in the voltage variance. This difference will more than likely be swamped out by process variations, such as mismatch. The well resistors tend to have less process variations for the same size resistor and area, because their density is higher and they can make their widths wider.

General Bandgap Notes Basic Bandgap Topology

# **Basic Bandgap Topology**

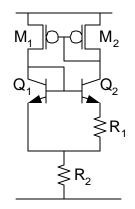

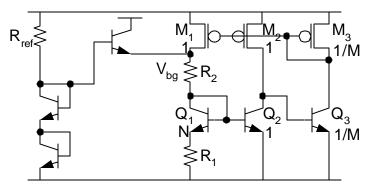

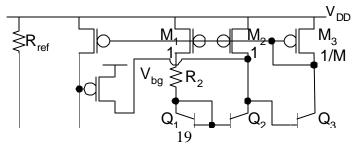

One of the simplest bandgap and lowest noise bandgap topologies is shown in the following figure. As with all bandgap topologies, it consists a PTAT current generator, which is dropped across a resistor to generate a boosted PTAT voltage. The boosted PTAT voltage is added to the base-emitter voltage of Q1 to realize a bandgap voltage. An advantage of this topology is the bias current for the PTAT generator is shared with the bandgap resistor, R2, which also reduces the required value and noise of R2 by a factor of two.

Fig. 1: Basic BiCMOS bandgap with Q1 diode connected.

The disadvantages of this topology in this simplified form, is a weak dependence on power supply voltage, some base current effects, a limitation to a BiCMOS process, and the lack of start-up circuitry. These disadvantages can be overcome with some minor structural changes, which will be evolored later in the report 7

Bandgap Design and Analysis When developing bandgap structures a common question arises: "Which side do I diode connect the diode voltages?" Diode connection of either side yields the correct DC value to generate a bandgap voltage, but connection to the resistor side yields an unstable bandgap for this topology. We can see this by looking at the loop gains. The loop gain of the basic bandgap is

$$A_{L} = \frac{-g_{mQ2}}{1 + g_{mQ2} \cdot R_{1}} \cdot \frac{1}{g_{mM2}} \cdot -g_{mM2} \cdot \frac{1}{g_{mQ1}} = \frac{1}{1 + g_{mQ2} \cdot R_{1}}$$

if diode connected around  $Q_1$ . If  $Q_2$  is diode connected the loop gain is:

$$A_{L} = -g_{mQ1} \cdot \frac{1}{g_{mM1}} \cdot -g_{mM2} \cdot \left(\frac{1}{g_{mQ2}} + R_{1}\right) = 1 + g_{mQ1} \cdot R_{1}$$

In both cases we see the loop gain is positive, and thus must be less than one to be stable. We must diode connect  $Q_1$  to make the loop gain less than one to insure stability around the loop.

Basic Bandgap Topology

Bandgap Design Equations

#### **Design Equations**

For design, we assume a usage of the basic bandgap topology described above. First, measurure  $V_{BE}$  at  $T=T_0$ , call this  $V_{BE0}$ . Using the equations developed above, a value for  $K_{ptat}$  can be determined:

$\ln(EG) = \frac{V_{BE0} - V_{G0}}{V_{T0}}$ Thus  $K_{\text{ptat}} = (\gamma - \alpha) - \ln(\text{EG})$  can be simplified to

$$K_{\text{ptat}} = \frac{V_{\text{G0}} - V_{\text{BE0}}}{V_{\text{T0}}} + (\gamma - \alpha)$$

Start by with KVL to find the output voltage

$$V_o = V_{BE5} + 2 \cdot I \cdot R_2$$

Subtituting for I:

$$I = \frac{V_{BE5} - V_{BE4}}{R_1} = \frac{V_T \cdot \ln(N)}{R_1}$$

$V_0 = V_{BE5} + 2 \cdot V_T \cdot \ln(N) \cdot \frac{R_2}{R_1}$

Set this equal to the general purpose bandgap equation,  $V_0 = V_{BE} + K_{ptat} \cdot V_T$ , now

$K_{\text{ptat}} = 2 \cdot \ln(N) \cdot R2_R1$

thus for design, where the subscript, 0, implies these numbers are at  $T_0$ .

$$R2_R1 = \frac{K_{ptat}}{2 \cdot \ln(N)} = \frac{\frac{V_{G0} - V_{BE50}}{V_{T0}} + (\gamma - \alpha)}{2 \cdot \ln(N)}$$

Bandgap Design Equations

Headroom Constraints

#### **Bandgap Headroom Constraints**

The first step of most device sizing procedures is to define headroom constraints, which often fixes the values

Randgany Design and Herelysis requires knowledge of the maximum and miminum values for the bandgap voltage.

$V_{bgmax} := V_{bg'} (1 + \sigma_{\Delta V bg_V bg})$

$V_{bgmax} = 1.32 V$

When sizing the PMOS current mirror for the bandgap it is desirable to make the  $V_{DSsatP}$  as large as possible to reduce it's noise contribution to the output. There are two headrom constraints, which limit the size the  $V_{DSsatP}$ . The first constraint on  $V_{DSsatP}$  is set when the one of the PMOS transistors goes into the linear region.

$V_{DSsatP} \coloneqq V_{DDmin} - V_{bgmax}$

$V_{DSsatP} = 1.38 V$

The constraint is to prevent one of the bipolar transistors from going into saturation. This is almost always the tougher constaint as  $V_{TPmax}+V_{CEsat}$  is usually greater than  $V_{BEmin}$ .

$V_{DSsatP} := V_{DDmin} - V_{TPmax} - V_{bgmax} + V_{BEmin} - V_{CEsat}$

$V_{DSsatP} = 0.78 V$

If a emitter follower is used to reduce the effects of base current, the  $V_{DSsatP}\mbox{'s}$  of the PMOS devices must be reduced

$V_{DSsatP} := if(BetaHelper = 1, V_{DDmin} - V_{TPmax} - V_{bgmax} - V_{CEsat}, V_{DSsatP})$   $V_{DSsatP} = 0.78 V$

Using a minimum desired  $V_{DSsat}$  we can determine the minimum supply voltage for this topology:

$V_{DDbgmin} \coloneqq if \Big( BetaHelper = 1, V_{bgmax} + V_{DSsatmin} + V_{CEsat} + V_{TPmax}, V_{bgmax} + V_{DSsatmin} + V_{CEsat} + V_{TPmax} - V_{BEmin} \Big)$

$V_{DDbgmin} = 2.12 V$

Headroom Constraints

BiCMOS Bandgap Noise Analysis

# Noise Analysis of BiCMOS Bandgap

When calculating the noise from the bandgap, one must ask what is important: integrated noise or noise amplitude at a given frequency. Usually the answer is integrated noise, but in this case the bandwidth is usually set by another circuit and the noise amplitude by the bandgap circuit. Thus the noise at a given frequency is most important for bandgaps. The next question is which frequency? Bandgaps are usually built with BJT devices, which exhibit 1/f noise corners in the 1kHz range, which is negligible for most applications, and so are dominated by 1/f noise of the current mirror for low frequencies.

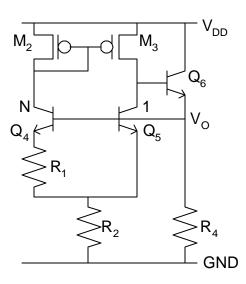

Fig. 1: BiCMOS Bandgap Voltage Circuit

The required noise level for the bandgap can be given directly, or found from a SNDR and BW specification:

$\sigma_{\text{Von}} \coloneqq V_{\text{bg}} \cdot 10^{-20}$

Bardene Fridgereid Archeite

$$v_n := if \left( \text{Find}_{vn_from} \text{SNDR}, \sqrt{\frac{\sigma_{Von}^2}{BW}}, v_n \right)$$

$v_n = 41.44 \frac{nV}{\sqrt{Hz}}$

Distributed Voltage Noise

There are four equations and four unknowns for the four main nodes of the circuit.  $\mathbf{1}$

$$\begin{aligned} \mathbf{v}_{G3} &= \mathbf{v}_{nM3} - g_{mQ3} \cdot \frac{1}{g_{mM3}} \cdot \left(\mathbf{v}_{B3} + \mathbf{v}_{nQ3}\right) \\ \mathbf{v}_{B1} &= \mathbf{v}_{nQ1} + \mathbf{v}_{nR1} - g_{mM1} \cdot \left(\mathbf{v}_{G3} + \mathbf{v}_{nM1}\right) \cdot \left(\frac{1}{g_{mQ1}} + \mathbf{R}_{1}\right) \\ \mathbf{v}_{B3} &= -\left[g_{mM2} \cdot \left(\mathbf{v}_{G3} + \mathbf{v}_{nM2}\right) + g_{mQ2} \cdot \left(\mathbf{v}_{B1} + \mathbf{v}_{nQ2}\right)\right] \cdot \mathbf{R}_{o} \\ \mathbf{v}_{bg} &= \mathbf{v}_{B1} - g_{mM1} \cdot \left(\mathbf{v}_{G3} + \mathbf{v}_{nM1}\right) \cdot \mathbf{R}_{2} + \mathbf{v}_{nR2} \end{aligned}$$

These equations are simplified to solve for the bandgap voltage Given

$$\begin{split} v_{G3} &= v_{nM3} - \frac{g_{mQ1}}{M} \cdot \frac{M}{g_{mM1}} \cdot (v_{B3} + v_{nQ3}) \\ v_{B1} &= v_{nQ1} + v_{nR1} - \frac{g_{mM1}}{g_{mQ1}} \cdot (v_{G3} + v_{nM1}) \cdot (1 + \ln(N)) \\ v_{B3} &= -\left[g_{mM1} \cdot (v_{G3} + v_{nM2}) + g_{mQ1} \cdot (v_{B1} + v_{nQ2})\right] \cdot R_{o} \\ v_{bg} &= v_{B1} - g_{mM1} \cdot (v_{G3} + v_{nM1}) \cdot R_{2} + v_{nR2} \end{split}$$

Find $\left(v_{G3}, v_{B1}, v_{B3}, v_{bg}\right) \rightarrow \left[ \frac{-R_{o} \cdot g_{mQ1}^{2} \cdot v_{nR1} - \ln(8) \cdot v_{nM3} \cdot g_{mM1} - R_{o} \cdot g_{mQ1}^{2} \cdot v_{nQ2} - R_{o} \cdot g_{mQ1}^{2} \cdot v_{nQ1} + v_{nR2} \cdot g_{mQ1} + R_{2} \cdot g_{mQ1}}{\left(\frac{g_{mM1}}{g_{mQ1}}\right)^{2} \cdot (1 + g_{mQ1} \cdot R_{1})^{2} \cdot 2 \cdot v_{nM1}^{2} + \left[ (1 + R_{1} \cdot g_{mQ1})^{2} + 1 \right] \cdot v_{nQ1}^{2} + v_{nR1}^{2}} \end{split}$

$$v_{B1} = \frac{(R_2 \cdot g_m + 1)^2 \cdot v_{nR1}^2 + (1 + R_2 \cdot g_m + \ln(N))^2 \cdot v_{nQ2}^2 + (R_2 \cdot g_m + 1)^2 \cdot v_{nQ1}^2 + (\frac{g_m M_1}{g_m})^2 \cdot (1 + R_2 \cdot g_m + \ln(N))^2 \cdot 2 \cdot v_{nM1}^2}{\ln(N)^2} + \frac{(1 + R_2 \cdot g_m + \ln(N))^2 \cdot 2 \cdot v_{nM1}^2}{\ln(N)^2} + \frac{(1 + R_2 \cdot g_m + \ln(N))^2 \cdot 2 \cdot v_{nM1}^2}{\ln(N)^2} + \frac{(1 + R_2 \cdot g_m + \ln(N))^2 \cdot 2 \cdot v_{nM1}^2}{\ln(N)^2} + \frac{(1 + R_2 \cdot g_m + \ln(N))^2 \cdot 2 \cdot v_{nM1}^2}{\ln(N)^2} + \frac{(1 + R_2 \cdot g_m + \ln(N))^2 \cdot 2 \cdot v_{nM1}^2}{\ln(N)^2} + \frac{(1 + R_2 \cdot g_m + \ln(N))^2 \cdot 2 \cdot v_{nM1}^2}{\ln(N)^2} + \frac{(1 + R_2 \cdot g_m + \ln(N))^2 \cdot 2 \cdot v_{nM1}^2}{\ln(N)^2} + \frac{(1 + R_2 \cdot g_m + \ln(N))^2 \cdot 2 \cdot v_{nM1}^2}{\ln(N)^2} + \frac{(1 + R_2 \cdot g_m + \ln(N))^2 \cdot 2 \cdot v_{nM1}^2}{\ln(N)^2} + \frac{(1 + R_2 \cdot g_m + \ln(N))^2 \cdot 2 \cdot v_{nM1}^2}{\ln(N)^2} + \frac{(1 + R_2 \cdot g_m + \ln(N))^2 \cdot 2 \cdot v_{nM1}^2}{\ln(N)^2} + \frac{(1 + R_2 \cdot g_m + \ln(N))^2 \cdot 2 \cdot v_{nM1}^2}{\ln(N)^2} + \frac{(1 + R_2 \cdot g_m + \ln(N))^2 \cdot 2 \cdot v_{nM1}^2}{\ln(N)^2} + \frac{(1 + R_2 \cdot g_m + \ln(N))^2 \cdot 2 \cdot v_{nM1}^2}{\ln(N)^2} + \frac{(1 + R_2 \cdot g_m + \ln(N))^2 \cdot 2 \cdot v_{nM1}^2}{\ln(N)^2} + \frac{(1 + R_2 \cdot g_m + \ln(N))^2 \cdot 2 \cdot v_{nM1}^2}{\ln(N)^2} + \frac{(1 + R_2 \cdot g_m + \ln(N))^2 \cdot 2 \cdot v_{nM1}^2}{\ln(N)^2} + \frac{(1 + R_2 \cdot g_m + \ln(N))^2 \cdot 2 \cdot v_{nM1}^2}{\ln(N)^2} + \frac{(1 + R_2 \cdot g_m + \ln(N))^2 \cdot 2 \cdot v_{nM1}^2}{\ln(N)^2} + \frac{(1 + R_2 \cdot g_m + \ln(N))^2 \cdot 2 \cdot v_{nM1}^2}{\ln(N)^2} + \frac{(1 + R_2 \cdot g_m + \ln(N))^2 \cdot 2 \cdot v_{nM1}^2}{\ln(N)^2} + \frac{(1 + R_2 \cdot g_m + \ln(N))^2 \cdot 2 \cdot v_{nM1}^2}{\ln(N)^2} + \frac{(1 + R_2 \cdot g_m + \ln(N))^2 \cdot 2 \cdot v_{nM1}^2}{\ln(N)^2} + \frac{(1 + R_2 \cdot g_m + \ln(N))^2 \cdot 2 \cdot v_{nM1}^2}{\ln(N)^2} + \frac{(1 + R_2 \cdot g_m + \ln(N))^2 \cdot 2 \cdot v_{nM1}^2}{\ln(N)^2} + \frac{(1 + R_2 \cdot g_m + \ln(N))^2 \cdot 2 \cdot v_{nM1}^2}{\ln(N)^2} + \frac{(1 + R_2 \cdot g_m + \ln(N))^2 \cdot 2 \cdot v_{nM1}^2}{\ln(N)^2} + \frac{(1 + R_2 \cdot g_m + \ln(N))^2 \cdot 2 \cdot v_{nM1}^2}{\ln(N)^2} + \frac{(1 + R_2 \cdot g_m + \ln(N))^2 \cdot 2 \cdot v_{nM1}^2}{\ln(N)^2} + \frac{(1 + R_2 \cdot g_m + \ln(N))^2 \cdot 2 \cdot v_{nM1}^2}{\ln(N)^2} + \frac{(1 + R_2 \cdot g_m + \ln(N))^2 \cdot 2 \cdot v_{nM1}^2}{\ln(N)^2} + \frac{(1 + R_2 \cdot g_m + \ln(N))^2 \cdot 2 \cdot v_{nM1}^2}{\ln(N)^2} + \frac{(1 + R_2 \cdot g_m + \ln(N))^2 \cdot 2 \cdot v_{nM1}^2}{\ln(N)^2} + \frac{(1 + R_2 \cdot g_m + \ln(N))^2 \cdot 2 \cdot v_{nM1}^2}{\ln(N)^2} + \frac{(1 + R_2 \cdot g_m + \ln$$

An important variable is the PTAT coefficient,  $\mathbf{K}_{\text{ptat}}$ :

$$\begin{split} K_{\text{ptat}} &= \frac{V_{\text{G0}} - V_{\text{BE0}}}{V_{\text{T}}} + (\gamma - \alpha) \\ \alpha &\coloneqq 1 - \text{RTC} \cdot \text{Temp} \qquad \alpha = 0.36 & \text{Current Source Temperature Coefficient} \\ \mu_{\text{N}} &= \text{C} \cdot \text{T}^{-n} = \text{C} \cdot \text{T}_{0}^{-n} \cdot \left(\frac{\text{T}}{\text{T}_{0}}\right)^{-n} \text{n} \coloneqq 0.8 & \text{Electron Mobility as a function of Temperature} \\ \gamma &\coloneqq 4 - n & \gamma = 3.2 & \text{where } V_{\text{RE0}} \text{ is the diode voltage at the nominal operating temperature, and nominal operating current. a is the} \end{split}$$

Bandgap Design and Analysis resistor temperature coefficient.

A potential inaccuracy of the design procedure developed here is that  $K_{ptat}$  requires a value for  $V_{BE0}$ ,  $V_{BE0}$ requires are value for current, I, and the catch 22 continues with I requiring a value of K<sub>ptat</sub>. The exact solution involves iteration of the nonlinear equations. To resolve this conflict, we guess at the current to solve for V<sub>BE0</sub>, and solve for the current. We then recalculate  $V_{BE0}$  to find the resistor values. Here we use an initial estimate of I to be 100mA.

$$V_{BE0} \coloneqq V_T \cdot \ln \left( \frac{100 \mu A}{I_s} \right) \qquad V_{BE0} = 0.74 V$$

$$K_{ptat} \coloneqq \frac{V_{G0} - V_{BE0}}{V_T} + (\gamma - \alpha) \qquad K_{ptat} = 20.17$$

Making the following substitutions

$$g_{mQ1} = g_{m} = \frac{I}{V_{T}} v_{nQ1}^{2} = v_{nQ2}^{2} = 4 \cdot k \cdot \text{Temp} \cdot \frac{V_{T}}{2 \cdot I} \qquad v_{nR1}^{2} = 4 \cdot k \cdot \text{Temp} \cdot \frac{V_{T} \cdot \ln(N)}{I} \quad v_{nR2}^{2} = 4 \cdot k \cdot \text{Temp} \cdot R_{2}$$

$$R_{1} = \frac{V_{T} \cdot \ln(N)}{I} \qquad g_{mM1} = \frac{2 \cdot I}{V_{DSsatP}} \qquad v_{nM1}^{2} = 4 \cdot k \cdot \text{Temp} \cdot \frac{2}{3 \cdot \frac{2 \cdot I}{V_{DSsat}}} \qquad \frac{R_{2}}{R_{1}} = \frac{K_{ptat}}{2 \cdot \ln(N)}$$

$$v_{n}^{2} = 4 \cdot k \cdot \text{Temp} \cdot \frac{V_{T}}{I} \cdot \left[ \left( \frac{R_{2}}{R_{1}} + \frac{1}{\ln(N)} \right)^{2} \cdot \ln(N) + \left( \frac{1}{\ln(N)} + \frac{R_{2}}{R_{1}} + 1 \right)^{2} \cdot \frac{1}{2} + \left( \frac{R_{2}}{R_{1}} + \frac{1}{\ln(N)} \right)^{2} \cdot \frac{1}{2} + \left( \frac{2 \cdot V_{T}}{V_{DSsatP}} \right)^{2} \cdot \left( \frac{1}{\ln(N)} + \frac{R_{2}}{R_{1}} + 1 \right)^{2} \cdot \frac{1}{2} + \left( \frac{R_{2}}{R_{1}} + \frac{1}{\ln(N)} \right)^{2} \cdot \frac{1}{2} + \left( \frac{2 \cdot V_{T}}{V_{DSsatP}} \right)^{2} \cdot \left( \frac{1}{\ln(N)} + \frac{R_{2}}{R_{1}} + 1 \right)^{2} \cdot \frac{1}{2} + \left( \frac{R_{2}}{R_{1}} + \frac{1}{\ln(N)} \right)^{2} \cdot \frac{1}{2} + \left( \frac{R_{2}}{R_{1}} + \frac{1}{\ln(N$$

$$I := 4 \cdot k \cdot \text{Temp} \cdot \frac{V_T}{v_n^2} \cdot \frac{K_{\text{ptat}}^2}{2 \cdot \ln(N)}$$

$$I = 26.21 \,\mu\text{A}$$

From the current design equation we see that we want to increase V<sub>BE0</sub>, to increase K<sub>ptat</sub>, to reduce the current drain requirements. This means using small transistors. In practice there is a trade-off for device size, as small transistors increase the base resistance and the noise.

Solving for I without assumptions:

$$I := 4 \cdot k \cdot \text{Temp} \cdot \frac{V_{\text{T}}}{V_{\text{n}}^{2}} \cdot \left[ \left( \frac{K_{\text{ptat}}}{2 \cdot \ln(N)} + \frac{1}{\ln(N)} \right)^{2} \cdot \ln(N) + \left( \frac{1}{\ln(N)} + \frac{K_{\text{ptat}}}{2 \cdot \ln(N)} + 1 \right)^{2} \cdot \frac{1}{2} + \left( \frac{K_{\text{ptat}}}{2 \cdot \ln(N)} + \frac{1}{\ln(N)} \right)^{2} \cdot \frac{1}{2} + \left( \frac{2 \cdot V_{\text{T}}}{V_{\text{DSsatP}}} \right)^{2} \cdot \left( \frac{1}{\ln(N)} + \frac{1}{2 \cdot \ln(N)} + \frac{1}{2 \cdot \ln(N)} + \frac{1}{2 \cdot \ln(N)} \right)^{2} \cdot \frac{1}{2} + \left( \frac{2 \cdot V_{\text{T}}}{V_{\text{DSsatP}}} \right)^{2} \cdot \left( \frac{1}{\ln(N)} + \frac{1}{2 \cdot \ln(N)} + \frac{1}{2 \cdot \ln(N)} + \frac{1}{2 \cdot \ln(N)} \right)^{2} \cdot \frac{1}{2} + \left( \frac{1}{2 \cdot \ln(N)} + \frac{1}{2 \cdot \ln(N)} + \frac{1}{2 \cdot \ln(N)} \right)^{2} \cdot \frac{1}{2} + \left( \frac{1}{2 \cdot \ln(N)} + \frac{1}{2 \cdot \ln(N)} \right)^{2} \cdot \frac{1}{2} + \left( \frac{1}{2 \cdot \ln(N)} + \frac{1}{2 \cdot \ln(N)} + \frac{1}{2 \cdot \ln(N)} \right)^{2} \cdot \frac{1}{2} + \left( \frac{1}{2 \cdot \ln(N)} + \frac{1}{2 \cdot \ln(N)} \right)^{2} \cdot \frac{1}{2} + \left( \frac{1}{2 \cdot \ln(N)} + \frac{1}{2 \cdot \ln(N)} \right)^{2} \cdot \frac{1}{2} + \left( \frac{1}{2 \cdot \ln(N)} + \frac{1}{2 \cdot \ln(N)} \right)^{2} \cdot \frac{1}{2} + \left( \frac{1}{2 \cdot \ln(N)} + \frac{1}{2 \cdot \ln(N)} \right)^{2} \cdot \frac{1}{2} + \left( \frac{1}{2 \cdot \ln(N)} + \frac{1}{2 \cdot \ln(N)} \right)^{2} \cdot \frac{1}{2} + \left( \frac{1}{2 \cdot \ln(N)} + \frac{1}{2 \cdot \ln(N)} \right)^{2} \cdot \frac{1}{2} + \left( \frac{1}{2 \cdot \ln(N)} + \frac{1}{2 \cdot \ln(N)} \right)^{2} \cdot \frac{1}{2} + \left( \frac{1}{2 \cdot \ln(N)} + \frac{1}{2 \cdot \ln(N)} \right)^{2} \cdot \frac{1}{2} + \left( \frac{1}{2 \cdot \ln(N)} + \frac{1}{2 \cdot \ln(N)} \right)^{2} \cdot \frac{1}{2} + \left( \frac{1}{2 \cdot \ln(N)} + \frac{1}{2 \cdot \ln(N)} \right)^{2} \cdot \frac{1}{2} + \left( \frac{1}{2 \cdot \ln(N)} + \frac{1}{2 \cdot \ln(N)} \right)^{2} \cdot \frac{1}{2} + \left( \frac{1}{2 \cdot \ln(N)} + \frac{1}{2 \cdot \ln(N)} \right)^{2} \cdot \frac{1}{2} + \left( \frac{1}{2 \cdot \ln(N)} + \frac{1}{2 \cdot \ln(N)} \right)^{2} \cdot \frac{1}{2} + \left( \frac{1}{2 \cdot \ln(N)} + \frac{1}{2 \cdot \ln(N)} \right)^{2} \cdot \frac{1}{2} + \left( \frac{1}{2 \cdot \ln(N)} + \frac{1}{2 \cdot \ln(N)} \right)^{2} \cdot \frac{1}{2} + \left( \frac{1}{2 \cdot \ln(N)} + \frac{1}{2 \cdot \ln(N)} \right)^{2} \cdot \frac{1}{2} + \left( \frac{1}{2 \cdot \ln(N)} + \frac{1}{2 \cdot \ln(N)} \right)^{2} \cdot \frac{1}{2} + \left( \frac{1}{2 \cdot \ln(N)} + \frac{1}{2 \cdot \ln(N)} \right)^{2} \cdot \frac{1}{2} + \left( \frac{1}{2 \cdot \ln(N)} + \frac{1}{2 \cdot \ln(N)} \right)^{2} \cdot \frac{1}{2} + \left( \frac{1}{2 \cdot \ln(N)} \right)^{2} \cdot \frac{1}{2} +$$

A more accurate way of calculating the current involves including the effects of 1/f noise and optimizing for cost, with a lower limit being set by the current required for thermal noise. 1/f noise can be decreased by increasing the device area without affecting current, so it is desirable to make the current as low as possible. Analysis has shown leaving 3dB margin for 1/f and thermal noise is usually close to the value to minimize overall cost.

$$\begin{split} I &:= if(No1_f = 1, I, 2 \cdot I) & I = 73.61 \, \mu A \\ & If I is constrained to a fixed value we replace the calculated current, with the constrained value. \\ I &:= I_{fix}(I) & I = 73.61 \, \mu A \end{split}$$

Solving for PMOS 1/f noise alone and making variable substitutions: 211-

$$v_{nM1}^{2} = \frac{K_{fP}}{W_{P} \cdot L_{P} \cdot f} \qquad \qquad W_{P} = \frac{2 \cdot P LP}{\mu_{P} \cdot C_{OX} \cdot V_{DSsatP}^{2}}$$

$$v_{bg1_{f}}^{2} = \left(\frac{2 \cdot V_{T}}{V_{DSsatP}}\right)^{2} \cdot \left(\frac{1}{\ln(N)} + \frac{K_{ptat}}{2 \cdot \ln(N)} + 1\right)^{2} \cdot 2 \cdot v_{nM1}^{2} = 4 \cdot V_{T}^{2} \cdot \left(\frac{1}{\ln(N)} + \frac{K_{ptat}}{2 \cdot \ln(N)} + 1\right)^{2} \cdot \frac{K_{fP} \cdot \mu_{P} \cdot C_{OX}}{I \cdot L_{P}^{2} \cdot f}$$

Solving for the required length given half of the noise is thermal noise:

$$\mathsf{Ba}_{\mathsf{LP1_f}} := \sqrt{4 \cdot \mathsf{V_T}^2 \cdot \left(\frac{1}{\ln(\mathsf{N})} + \frac{\mathsf{K_{ptat}}}{2 \cdot \ln(\mathsf{N})} + 1\right)^2 \cdot \frac{\mathsf{K_{fP}} \cdot \mu_{P} \cdot \mathsf{C}_{OX}}{I \cdot \frac{\mathsf{V_n}^2}{2} \cdot f} \, \mathsf{Lp1_f} = 0.45 \, \mu \mathsf{m}$$

Once the current is known for the bandgap, the resistor values can be found. This requires a recalculation of the  $K_{ptat}$  variable.

$$\begin{split} & V_{BE0} \coloneqq V_T \cdot \ln \left(\frac{I}{I_s}\right) & V_{BE0} = 0.73 V \\ & K_{ptat} \coloneqq \frac{V_{G0} - V_{BE0}}{V_T} + (\gamma - \alpha) & K_{ptat} = 20.47 \\ & R_1 \coloneqq \frac{V_T \cdot \ln(N)}{I} & R_1 = 0.76 \, \mathrm{k\Omega} & \text{Widlar Current Resistor} \\ & R_2 \coloneqq \frac{K_{ptat}}{2 \cdot \ln(N)} \cdot R_1 & R_2 = 3.73 \, \mathrm{k\Omega} & \text{Common Resistor} \end{split}$$

BiCMOS Bandgap Noise Analysis

Current Mirror Variance

# **Current Mirror Variance Derivation**

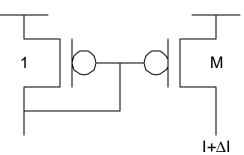

Fig. 1: Current mirror used to find variance

#### Inputs

| $I_{in} := 100 \mu A$                   | Input Current                               |

|-----------------------------------------|---------------------------------------------|

| M := 2                                  | <b>Current Mirror Ratio</b>                 |

| $\sigma_{\Delta I\_Ides} \coloneqq 2\%$ | <b>Matching Requirement</b>                 |

| $V_{DSsat} := 0.3V$                     | <b>V</b> <sub>DSsat</sub> of Current Mirror |

#### Derivation

Before we calculate the variance in the bandgap, it is useful to find the variance in a weighted current mirror. First we start with a basic MOSFET equation for the diode connected portion of the mirror.

$$I_{in} = \mu \cdot C_{OX} \cdot \frac{W}{L} \cdot (V_{GS} - V_T)^2 \qquad I_{out} = M \cdot I_{in} + \Delta I$$

$$I_{out} := M \cdot I_{in} \qquad I_{out} = 200 \,\mu A$$

Now we write an equation for the output portion of the mirror. Here we add mismatches. The width is multiplied by M, by using M transistors the variance in widths of the transistor add to make the overall variance increase by sqrt(M).

$$I_{out} + \Delta I_{out} = \mu \cdot C_{OX} \cdot \frac{\left(M \cdot W_o + \sqrt{M} \cdot \Delta W\right)}{L + \Delta L} \left(V_{GS} - V_T + \Delta V_T\right)^2$$

These two equations can be combined to find the variance in the output of the current mirror.

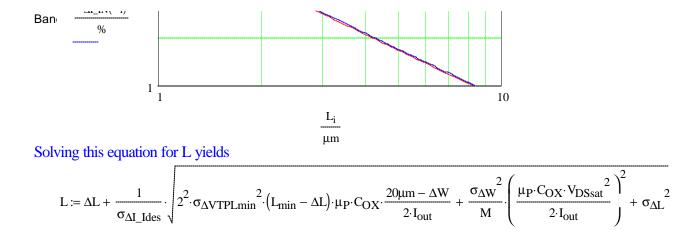

Ban

$$\sigma_{\Delta I\_Io}^{2} = \frac{2^{2} \cdot \sigma_{\Delta VT}^{2}}{V_{DSsat}^{2}} + \frac{1}{M} \cdot \frac{\sigma_{\Delta W}^{2}}{(W_{o} - \Delta W)^{2}} + \frac{\sigma_{\Delta L}^{2}}{(L - \Delta L)^{2}}$$

From this equation it would imply that large  $V_{DSsat}$  improves current source matching, but we will see this is not true later. Now W is usually sized given L,  $V_{DSsat}$ , and I

$$W_{o} = \frac{2 \cdot I_{out} \cdot (L - \Delta L)}{\mu \cdot C_{OX} \cdot V_{DSsat}^{2}} + \Delta W$$

Making this substitution yields:

$$\sigma_{\Delta I\_I}^{2} = \frac{2^{2} \cdot \sigma_{\Delta VT}^{2}}{V_{DSsat}^{2}} + \frac{\sigma_{\Delta W}^{2}}{M} \cdot \left[\frac{\mu \cdot C_{OX} \cdot V_{DSsat}^{2}}{2 \cdot I_{out} \cdot (L - \Delta L)}\right]^{2} + \frac{\sigma_{\Delta L}^{2}}{(L - \Delta L)^{2}}$$

This equation implies current source matching is achieved at an optimal  $V_{DSsat}$ . We will see this is also not true because we must also substitute an equation for  $\Delta V_T$ , which is also a function of L and  $V_{DSsat}$ .

$$\sigma_{\Delta \text{VTP}}(L) = 3 \cdot \left[ \frac{\sigma_{\text{VTPLmin}}}{3} \cdot \left( \frac{0.5 \cdot \mu \text{m} - \Delta L}{L - \Delta L} \right)^{n_{\text{P}}} + \frac{\left( \frac{L}{\text{m}} \right)^{n_{\text{P}}}}{a_{\text{P}}} \cdot \text{V} \right] \qquad 3\sigma \text{ PMOS Threshold Variation}$$

This equation from a process manufacturer shows two components of matching, which are a function of the length of a device and the spacing of the devices. The spacing term is insignificant for spacings below 0.3mm, so we will drop this term. The equation is also not a function of device width; it is fixed for 20mm transistors, so we will modify the equation to account for changing device widths below. The exponent is very close to 1/2, so we will use the square root instead.

$$\sigma_{\Delta VTP}(L) = \sigma_{VTPLmin} \cdot \sqrt{\left(\frac{L_{min} - \Delta L}{L - \Delta L}\right)} \left(\frac{20\mu m - \Delta W}{W - \Delta W}\right)$$

substituting in the constraint on W:

3σ PMOS Threshold Variation

$$\sigma_{\Delta VTP}(L) = \sigma_{VTPLmin} \cdot \frac{V_{DSsat}}{L - \Delta L} \cdot \sqrt{\left(L_{min} - \Delta L\right) \cdot \mu \cdot C_{OX} \cdot \frac{20\mu m - \Delta W}{2 \cdot I_{out}}}$$

Given a required specification on the threshold variance, we can find the required L.

$$L = \Delta L + \sigma_{VTPLmin} \cdot \frac{V_{DSsat}}{\sigma_{\Delta VTPdes}} \cdot \sqrt{\left(L_{min} - \Delta L\right) \cdot \mu_{P} \cdot C_{OX} \cdot \frac{20\mu m - \Delta W}{2 \cdot I_{out}}}$$

If we now substitute the  $V_T$  mismatch into the current mismatch equation

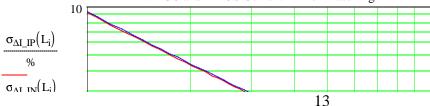

$$\sigma_{\Delta I\_IP}(L) \coloneqq \sqrt{2^2 \cdot \sigma_{\Delta VTPLmin}^2 \cdot \frac{(L_{min} - \Delta L)}{(L - \Delta L)^2} \cdot \mu_P \cdot C_{OX} \cdot \frac{20\mu m - \Delta W}{2 \cdot I_{out}} + \frac{\sigma_{\Delta W}^2}{M} \cdot \left[\frac{\mu_P \cdot C_{OX} \cdot V_{DSsat}^2}{2 \cdot I_{out} \cdot (L - \Delta L)^2}\right]^2 + \frac{\sigma_{\Delta L}^2}{(L - \Delta L)^2}}{(L - \Delta L)^2}$$

$$\sigma_{\Delta I\_IN}(L) \coloneqq \sqrt{2^2 \cdot \sigma_{\Delta VTNLmin}^2 \cdot \frac{(L_{min} - \Delta L)}{(L - \Delta L)^2} \cdot \mu_N \cdot C_{OX} \cdot \frac{20\mu m - \Delta W}{2 \cdot I_{out}} + \frac{\sigma_{\Delta W}^2}{M} \cdot \left[\frac{\mu_N \cdot C_{OX} \cdot V_{DSsat}^2}{2 \cdot I_{out} \cdot (L - \Delta L)^2}\right]^2 + \frac{\sigma_{\Delta L}^2}{(L - \Delta L)^2}$$

$$L_1 \coloneqq \frac{i}{num} \cdot 9.5\mu m + L_{min}$$

Length vector for plotting

NMOS and PMOS Current Mirror Matching

$$L = 4.17 \,\mu m$$

Normally, we think of larger  $V_{DSsat}$ s providing better current matching, but a larger  $V_{DSsat}$  requires a smaller width for a given current and length. The smaller width can hurt matching for small  $V_{DSsat}$ s. Also with smaller widths come smaller transistor area, which also hurts  $V_T$  matching. The net effect is  $DV_T$ 's effect on current mismatch is not affected by changes in  $V_{DSsat}$ . Another perspective is to plot the area required vs.  $V_{DSsat}$  for a given current matching constraint.

$$A := \frac{2^{2} \cdot \left(\frac{\sigma_{\Delta VTPLmin}}{V_{DSsat}}\right)^{2} \cdot \left(L_{min} - \Delta L\right) \cdot \left(20\mu m - \Delta W\right) + \frac{\sigma_{\Delta W}^{2}}{M} \cdot \frac{\mu_{P} \cdot C_{OX} \cdot V_{DSsat}^{2}}{2 \cdot I_{out}} + \frac{2 \cdot I_{out} \cdot \sigma_{\Delta L}^{2}}{\mu_{P} \cdot C_{OX} \cdot V_{DSsat}^{2}}}{\sigma_{\Delta L\_Ides}^{2}} \quad \sqrt{A} = 46.5 \, \mu m$$

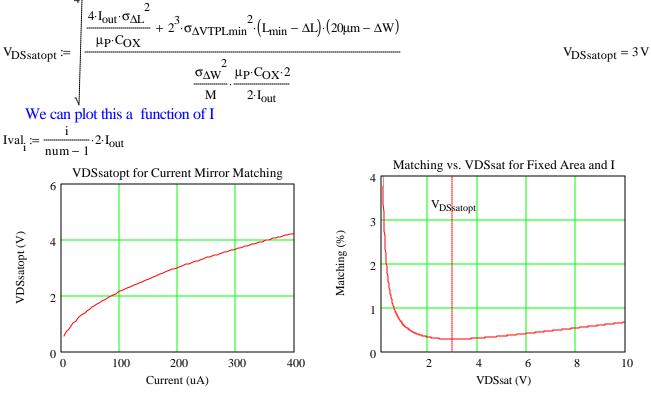

Here we see there is an optimal  $V_{DSsat}$  to minimize area for a given matching constraint:

We can also optimize current as to minimize area for a given matching constraint.

$I_{opt} \coloneqq \frac{1}{\sqrt{M}} \cdot \frac{\sigma_{\Delta W}}{\sigma_{\Delta L}} \cdot \frac{\mu_{P} \cdot C_{OX}}{2} \cdot V_{DSsat}^{2} \qquad I_{opt} = 2.03 \,\mu\text{A}$

We can also combine the optimal matching current and V<sub>DSsat</sub> equations to find the optimal current source

Bantching tosiginianizanalysis or a given matching constraint.

$$V_{DSsatopt} := \sqrt{\frac{4}{3}} \cdot \sqrt{M} \cdot \sigma_{\Delta VTPLmin} \cdot \sqrt{\frac{L_{min} - \Delta L}{\sigma_{\Delta L}}} \cdot \frac{20\mu m - \Delta W}{\sigma_{\Delta W}} \qquad V_{DSsatopt} = 0.37 V$$

$$I_{opt} := \sqrt{M} \cdot \mu_{P} \cdot C_{OX} \cdot \frac{2}{3} \cdot \frac{L_{min} - \Delta L}{\sigma_{\Delta L}} \cdot \frac{20\mu m - \Delta W}{\sigma_{\Delta L}} \cdot \sigma_{\Delta VTPLmin}^{2} \qquad I_{opt} = 3.05 \,\mu A$$

What we find is that most of these equations are not interesting for most applications, except maybe watch makers. For typical currents required by noise and settling time constraints, the optimal  $V_{DSsat}$ 's are larger than the ones optimal for dynamic range.

Improved matching required increased area, which reduces the bandwidth of the circuit it is attached. Below is an equation for the bandwidth of a current mirror of the a device given length.

$$\omega_{\rm T} = \frac{g_{\rm m}}{C_{\rm gs} + M \cdot C_{\rm gs}} = \frac{\mu \cdot V_{\rm DSsat}}{\left(L - \Delta L\right)^2 \cdot (M + 1)}$$

This can be solved for L and substitute into the current mismatch equation

$$L - \Delta L = \sqrt{\frac{\mu \cdot V_{\rm DSsat}}{\frac{\mu \cdot V_{\rm DSsat}}{2}}}$$

$$\omega_{\mathrm{T}} \coloneqq \frac{\sigma_{\Delta \mathrm{L} \mathrm{Ides}}^{2}}{\mathrm{M}+1} \cdot \frac{1}{\left[2^{2} \cdot \sigma_{\Delta \mathrm{VTPLmin}}^{2} \cdot \left(\mathrm{L_{min}} - \Delta \mathrm{L}\right) \cdot \frac{\mathrm{C}_{\mathrm{OX}}}{\mathrm{V}_{\mathrm{DSsat}}} \cdot \frac{20\mu\mathrm{m} - \Delta \mathrm{W}}{2 \cdot \mathrm{I}_{\mathrm{out}}} + \frac{\sigma_{\Delta \mathrm{W}}^{2}}{\mathrm{M} \cdot \mathrm{\mu}_{\mathrm{P}} \cdot \mathrm{V}_{\mathrm{DSsat}}^{2}} \cdot \left(\frac{\mathrm{\mu}_{\mathrm{P}} \cdot \mathrm{C}_{\mathrm{OX}} \cdot \mathrm{V}_{\mathrm{DSsat}}^{2}}{2 \cdot \mathrm{I}_{\mathrm{out}}}\right)^{2} + \frac{\sigma_{\Delta \mathrm{L}}^{2}}{\mathrm{\mu}_{\mathrm{P}} \cdot \mathrm{V}_{\mathrm{DSsat}}}\right] \frac{\omega_{\mathrm{T}}}{2 \cdot \mathrm{I}_{\mathrm{out}}} = 8.24 \,\mathrm{MHz}$$

Thus we can see a fast degradation of  $w_T$  as mismatch requirements increase.  $V_{DSsat}$  can also be optimized to maximize  $w_T$ , given matching and current requirements

$$V_{DSsat} \coloneqq \sqrt{\frac{M+1}{3} \cdot \left[\frac{\left(2 \cdot I_{out}\right)^2 \cdot \sigma_{\Delta L}^2}{C_{OX}^2 \cdot \mu_P^2 \cdot \sigma_{\Delta W}^2} + 2^2 \cdot \sigma_{\Delta VTPLmin}^2 \cdot 2 \cdot I_{out} \cdot \left(L_{min} - \Delta L\right) \cdot \frac{20\mu m - \Delta W}{\mu_P \cdot C_{OX} \cdot \sigma_{\Delta W}^2}\right]} \quad V_{DSsat} = 2.53 \text{ V}$$

One of the best ways to use these design equations to choose a current, I, and length, L, to provide the desired matching and bandwidth. It is difficult to come up with a neat closed form expression for I, but rather it is done here in the form of a quadratic

$$\begin{bmatrix} \sigma_{\Delta I\_Ides}^{2} - \frac{\sigma_{\Delta L}^{2}}{\frac{\mu \cdot V_{DSsat}}{\omega_{T} \cdot (M+1)}} \end{bmatrix} \cdot I_{out}^{2} = 2^{2} \cdot \sigma_{\Delta VTPLmin}^{2} \cdot \frac{(L_{min} - \Delta L)}{\frac{\mu \cdot V_{DSsat}}{\omega_{T} \cdot (M+1)}} \cdot \mu \cdot C_{OX} \cdot \frac{20\mu m - \Delta W}{2} \cdot I_{out} + \frac{\sigma_{\Delta W}^{2}}{M \cdot \frac{\mu \cdot V_{DSsat}}{\omega_{T} \cdot (M+1)}} \cdot \frac{\mu \cdot C_{OX} \cdot V_{DSsat}}{\omega_{T} \cdot (M+1)} \cdot \frac{\mu \cdot V_{DSsat}}{\omega_{T} \cdot (M+1)} \cdot \frac$$

Current Mirror Variance

# **Bandgap Voltage Variance Derivation**

Random Component Variations

$$I_{4} = I \qquad I_{5} = I + \Delta I \qquad \qquad I_{S5} = I_{S} \quad I_{S4} = N \cdot I_{S} \cdot \left(1 + \frac{\Delta I_{S}}{\sqrt{N}}\right)$$

$$R_{1} = R \qquad R_{2} = \frac{K_{ptat}}{2 \cdot \ln(N)} \cdot R \cdot \left(1 + \frac{\Delta R}{R \cdot \sqrt{\frac{K_{ptat}}{2 \cdot \ln(N)}}}\right)$$

<u>PTAT Current Generator Variance:</u>, Sum of the voltages around a loop

$V_{BE4} + R_1 \cdot I_4 = V_{BE5}$

$$I_{4} = \frac{V_{BE5} - V_{BE4}}{R_{1}} = \frac{V_{T} \cdot \ln\left(\frac{I_{4}}{I_{54}}\right) + V_{T} \cdot \ln\left(\frac{I_{5}}{N \cdot I_{55}}\right)}{R_{1}} = \frac{V_{T} \cdot \ln\left[\frac{I \cdot \left(1 - \frac{\Delta I}{2 \cdot I}\right)}{I_{5}}\right] + V_{T} \cdot \ln\left[\frac{I \cdot \left(1 + \frac{\Delta I}{2 \cdot I}\right)}{N \cdot I_{5} \cdot \left(1 - \frac{\sigma_{\Delta IS} IS}{\sqrt{N}}\right)}\right]}{R_{1}}$$

$$I_{4} = \frac{V_{T} \cdot \sqrt{\sigma_{\Delta I} I_{1}}^{2} + \frac{\sigma_{\Delta IS} I_{5}}{N} + V_{T} \cdot \ln(N)}{R_{1}}$$

$$I = \frac{V_{T} \cdot \left(-\sigma_{\Delta I} I_{1} + \frac{\sigma_{\Delta IS} IS}{N}\right) + V_{T} \cdot \ln(N)}{R_{1}}$$

The variance for the output voltage is given as follows

$V_{bg} = V_{BE5} + (I_4 + I_5) \cdot R_2$

Substitute in the variables and simplify:

$$\sigma_{\Delta V bg} V bg^{2} = V_{T}^{2} \cdot \left[ \left( 1 + \frac{1}{\ln(N)} + \frac{I \cdot R_{2}}{V_{T}} \right)^{2} \cdot \sigma_{\Delta I} I mir^{2} + \sigma_{\Delta Is} Is^{2} \cdot \left( \frac{K_{ptat}}{\ln(N) \cdot \sqrt{N}} \right)^{2} + \sigma_{\Delta R} R^{2} \cdot K_{ptat} \cdot 2 \cdot \ln(N) \right]$$

The variance in K is given as

$$\sigma_{\Delta K\_K} = \frac{1}{\ln(N)} \cdot \sqrt{\sigma_{\Delta I\_I}^2 + \frac{\sigma_{\Delta IS\_IS}^2}{N} + \ln(N)^2 \cdot \sigma_{\Delta R\_R}^2}$$

For design we substitute the following variables:

$$\sigma_{\Delta R_{-}R}^{2} = \frac{\sigma_{\Delta R_{-}R,\min}^{2} \cdot W_{\min}^{2}}{W_{R}^{2}} \text{ where } \sigma_{\Delta R_{-}R,\min} \coloneqq \sqrt{\left(\frac{\frac{R_{sq} \cdot \sigma_{\Delta L}}{R_{1}}\right)^{2} + \sigma_{\Delta W}^{2}}{W_{\min}^{2}}} \sigma_{\Delta R_{-}R,\min} = 0.26$$

$$\sigma_{\Delta VTP}^{2} = \Delta V_{thPLmin}^{2} \cdot \frac{L_{min}^{2}}{L_{p}^{2}} \text{ 3s PMOS Threshold Variation, where}$$

$$\Delta V_{thPLmin} \coloneqq \sqrt{\sigma_{\Delta VTPLmin}^{2} \cdot V_{DSsat}^{2} \cdot \mu_{P} \cdot C_{OX} \cdot \frac{20\mu m}{2 \cdot 1 \cdot L_{min}}} \Delta V_{thPLmin} = 68.3 \text{ mV}$$

$$\sigma_{\Delta VTN}^{2} = \Delta V_{thLnmin}^{2} \cdot \frac{L_{min}^{2}}{L_{N}^{2}} \text{ 3s NMOS Threshold Variation, where}$$

$$\Delta V_{thNLmin} \coloneqq \sqrt{\sigma_{\Delta VTNLmin}^{2} \cdot V_{DSsat}^{2} \cdot \mu_{N} \cdot C_{OX} \cdot \frac{20\mu m}{2 \cdot 1 \cdot L_{m}}} \Delta V_{thNLmin} = 97.3 \text{ mV}$$

Ban

$$\sigma_{\Delta I\_Imir}^{2} = \Delta V_{thPLmin}^{2} \cdot \frac{L_{min}^{2}}{L_{P}^{2}} \cdot \left(\frac{2}{V_{DSsatP}}\right)^{2} + \sigma_{\Delta W}^{2} \cdot \left(\frac{\mu_{P} \cdot C_{OX} \cdot V_{DSsatP}^{2}}{2 \cdot I \cdot L_{P}}\right)^{2} + \frac{\sigma_{\Delta L}^{2}}{L_{P}^{2}} \text{ dimensional metric of the set of$$

$\sigma_{\Delta Is\_Is}^{2} = \sigma_{\Delta Is\_IsAreamin}^{2} \cdot \frac{\text{Area}_{BJTmin}}{\text{Area}_{Q1}}$

Thus the mismatch equation becomes

$$\sigma_{\Delta V bg\_V bg}^{2} = \frac{V_{T}^{2}}{V_{bg}^{2}} \cdot \left[ \left(1 + \frac{1}{\ln(N)} + \frac{I \cdot R_{2}}{V_{T}}\right)^{2} \cdot \left[ \Delta V_{thPLmin}^{2} \cdot \frac{L_{min}^{2}}{L_{P}^{2}} \cdot \left(\frac{2}{V_{DSsatP}}\right)^{2} + \sigma_{\Delta W}^{2} \cdot \left(\frac{\mu_{P} \cdot C_{OX} \cdot V_{DSsatP}^{2}}{2 \cdot I \cdot L_{P}}\right)^{2} + \frac{\sigma_{\Delta L}^{2}}{L_{P}^{2}} \right] + \frac{\sigma_{\Delta I}^{2}}{L_{P}^{2}} \cdot \left(\frac{2}{V_{DSsatP}}\right)^{2} + \frac{\sigma_{\Delta I}^{2}}{2 \cdot I \cdot L_{P}} + \frac{\sigma_{\Delta L}^{2}}{L_{P}^{2}} + \frac{\sigma_{\Delta I}^{2}}{L_{P}^{2}} + \frac{\sigma_{\Delta I}^{2}}{L_{P}^{2$$

The mismatch can be expressed in the following simplified form, which is useful for optimization:

$$\sigma_{\Delta V bg_V bg}^2 = \frac{X_1}{L_P^2} + \frac{X_2}{Area_{Q1}} + \frac{X_3}{W_R^2}$$

where the coefficients are

$$X_{1} \coloneqq \left(\frac{V_{T}}{V_{h\sigma}}\right)^{2} \cdot \left(1 + \frac{1}{\ln(N)} + \frac{I \cdot R_{2}}{V_{T}}\right)^{2} \cdot \left|\Delta V_{th}PLmin}^{2} \cdot L_{min}^{2} \cdot \left(\frac{2}{V_{DSsatP}}\right)^{2} + \sigma_{\Delta W}^{2} \cdot \left(\frac{\mu_{P} \cdot C_{OX} \cdot V_{DSsatP}^{2}}{2 \cdot I}\right)^{2} + \sigma_{Z} \cdot \sqrt{X_{1}} = 2.95 \% \cdot \mu m$$

$$X_{2} \coloneqq \left(\frac{V_{T}}{V_{bg}}\right)^{2} \cdot \frac{\sigma_{\Delta Is\_IsAreamin}^{2} \cdot Area_{BJTmin} \cdot K_{ptat}^{2}}{\ln(N)^{2} \cdot N} \qquad \sqrt{X_{2}} = 1.63 \% \cdot \mu m$$

$$X_{3} \coloneqq \left(\frac{V_{T}}{V_{bg}}\right)^{2} \cdot \sigma_{\Delta R\_R.min}^{2} \cdot W_{min}^{2} \cdot K_{ptat} \cdot 2 \cdot \ln(N) \qquad \sqrt{X_{3}} = 5 \% \cdot \mu m$$

The main goal is to minimize total cost, which effectively achieved by minimized total area. Minimizing total area requires optimization routines. Minimizing total active area is a good approximation

Area =

$$2 \cdot \frac{2 \cdot I \cdot L_P}{\mu_P \cdot C_{OX} \cdot V_{DSsatP}^2} \cdot L_P + (N+1) \cdot Area_{Q1} + \frac{W_R^2}{R_{sq}} \cdot (R_1 + R_2)$$

The active area can be expressed in the following form, which is useful for optimization:

Area =

$$Y_1 \cdot L_P^2 + Y_2 \cdot Area_{Q1} + Y_3 \cdot W_R^2$$

where the coefficients are

$$Y_{1} \coloneqq \frac{2 \cdot I}{\mu_{P} \cdot C_{OX} \cdot V_{DSsatP}^{2}}$$

$$Y_{2} \coloneqq N + 1$$

$$Y_{3} \coloneqq \frac{R_{1} + R_{2}}{R_{sq}}$$

$$X_{1} = 2.67 \frac{\mu m}{\mu m}$$

$$\sqrt{Y_{1}} = 2.67 \frac{\mu m}{\mu m}$$

$$\sqrt{Y_{2}} = 3 \frac{\mu m}{\mu m}$$

$$\sqrt{Y_{2}} = 3 \frac{\mu m}{\mu m}$$

$$\sqrt{Y_{3}} = 1.5 \frac{\mu m}{\mu m}$$

Area Coefficient for BJT Area

$$\sqrt{Y_{3}} = 1.5 \frac{\mu m}{\mu m}$$

Area Coefficient for Resistor Width

From these variables we can find the minimum total active area using a previous derivation.

Area<sub>opt</sub> :=

$$\frac{\left(\sqrt{Y_1 \cdot X_1} + \sqrt{Y_2 \cdot X_2} + \sqrt{Y_3 \cdot X_3}\right)^2}{\sigma_{\Delta V bg} V bg^2} \qquad \sqrt{Area_{opt}} = 6.75 \,\mu m \qquad \text{Minimum Total Area}$$

The minimum total area is used to find the required resistor widths and MOSFET lengths for matching.

$$L_{p} \coloneqq \sqrt{\frac{\text{Area}_{\text{opt}}}{\sigma_{\Delta V \text{bg}} V \text{bg}}^{2} \cdot \frac{X_{2}}{Y_{2}}}} \qquad L_{p} \approx 1.11 \,\mu\text{m} \qquad \text{Optimal PMOS Device Length}}$$

$$Area_{Q1} \coloneqq \sqrt{\frac{\text{Area}_{\text{opt}}}{\sigma_{\Delta V \text{bg}} V \text{bg}}^{2} \cdot \frac{X_{3}}{Y_{3}}}} \qquad \sqrt{\text{Area}_{Q1}} \approx 2.74 \,\mu\text{m} \qquad \text{Optimal BJT Area}}$$

$\mathsf{Ban}'_{\mathsf{W}_{\mathsf{R}}} \coloneqq \sqrt{\frac{\operatorname{Area}_{\mathsf{opt}}}{\frac{\operatorname{Area}_{\mathsf{opt}}}{2} \cdot \frac{X_{1}}{Y_{1}}}} \qquad \mathsf{W}_{\mathsf{R}} = 1.58\,\mu\mathrm{m} \qquad \mathsf{Optimal Resistor Width}$

When sizing the length we have to meet both the 1/f noise constraint and the matching constraint, so here we pick the larger of the two. To minimize area when the length constraint is longer for 1/f noise, we should recalculate the required resistor and BJT areas for matching. With the exact length sizing known, we have place constraints based on the minimum length, and incremental values. These length constraints are calculated in the following function.

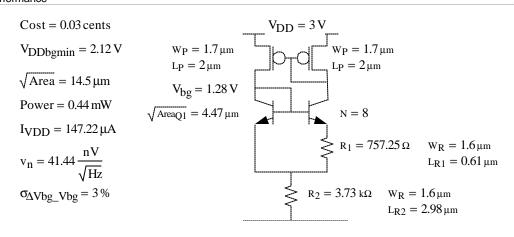

$$\begin{split} L_P &\coloneqq L_{fix} \Big[ \text{if} \Big[ \text{No1}_f, L_P, \max( (L_P \ L_{P1_f}) ) \Big] \Big] & L_P = 2 \, \mu m \\ W_R &\coloneqq W_{fix} \Big( W_R \Big) & W_R = 1.6 \, \mu m \\ \text{Area}_{Q1} &\coloneqq \text{Area}_{fix} \Big( \text{Area}_{Q1} \Big) & \sqrt{\text{Area}_{Q1}} = 4.47 \, \mu m \end{split}$$

## Other Sizing Calculations

With the PMOS length calculated, we can find the required PMOS lengths based on VDSsat and curret requirements:

$$\begin{split} W_{P} &\coloneqq \frac{2 \cdot L_{P}}{\mu_{P} \cdot C_{OX} \cdot (1 - \sigma_{\mu} p_{COX}) \cdot V_{DSsat}^{2}} \\ W_{P} &= 1.7 \mu m \end{split} \begin{array}{l} PMOS \ Transistor \ Width \\ W_{P} &\coloneqq W_{fix}(W_{P}) \\ W_{P} &\coloneqq W_{fi$$

Bandgap Variance Derivation

Start-Up Circuitry

## Start-Up Circuitry

Most self-bias circuits, such as bandgaps have two stable operating points. One of the stable operating states is the desired state and the other is typically a zero-current state. To prevent the zero-current state from occuring a start-up circuit is added, which is active during the undesired state and inactive during the desired state. The following figures illustrate several start-up circuits for the bandgap above. Simple modifications to these start-ups can be made for other bandgap topologies.

Fig. 1: Bandgap with Op-Amp Based Start-Up Circuit

The op-amp based start-up circuit has a simple design procedure:

- 1. Pick a bias voltage in the bandgap.

- 2. Find the two stable operating points for the bias voltage.

- 3. Set a compare voltage between the two stable operating voltages.

4. Amplify the difference and apply it to the gate of a transistor., so the transistor turns off for the desired operating point and turns on for the undesired. The transistor is used to inject current into the circuit in the undesired state. Here is another version of the circuit above:

Fig. 1: Sensitive Op-Amp Based Start-Up Circuit

Here the start-up circuit comparison voltage is from a node, which varies less than the in the previous circuit. With less variation in the comparison voltage, the circuit is more likely to switch to the wrong operating point with process variations and offsets in the amplifier. It is best to choose a node in the circuit with the largest variation between the two operating points. In bandgaps, this node is usually the bandgap voltage itself. The bandgap voltage difference between the two operating points is so large that the op-amp can be eliminated as in the following start-up circuit.

Fig. 1: Source Follower Based Start-Up Circuit

It is also possible to combine the reference voltage and the operational amplifier, or to use a compare current as in the following circuit.

Fig. 1: Current mirror based start-up circuit.

In all of the start-up examples above, the start-up circuit consumes static current. This current can be made small and thus unimportant relative to the current of the bandgap itself. It is possible to make the start-up consume zero current by making it bi-stable as well. If the bandgap is in it's desired state the start-up is forced into a zero current state. If the bandgap is in the undesired state, the startup circuit's current is active until the bandgap goes back to the desired state. This method for eliminating the current in the bandgap involves more risk, because the comparison point may shift when the start-up current is off.

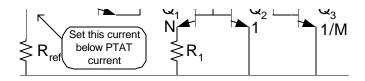

When a start-up circuit is used with a PTAT current generator, the internal voltage swings are usually too small to use without amplification. For PTAT current generators it is best to use a current mirror type of start-up circuit. Start-Up Circuitry

BiCMOS Bandgap Performance

## Area of Circuit

| $Area_{BJT} := (N + 1) \cdot Area_{Q1}$                                                                                                                         | $\sqrt{\text{Area}_{\text{BJT}}} = 13.42\mu\text{m}$ | BJT Area            |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|---------------------|

| $\operatorname{Area}_{\mathbf{R}} \coloneqq \operatorname{W}_{\mathbf{R}} \cdot \left( \operatorname{L}_{\mathbf{R}1} + \operatorname{L}_{\mathbf{R}2} \right)$ | $\sqrt{\text{Area}_{\text{R}}} = 2.4\mu\text{m}$     | Resistor Area       |

| Area <sub>CAP</sub> := $0\mu m^2$                                                                                                                               | $\sqrt{\text{Area}_{\text{CAP}}} = 0\mu\text{m}$     | Capacitor Area      |

| $\operatorname{Area}_{\operatorname{MOS}} \coloneqq 2 \cdot W_{\mathbf{P}} \cdot \left( L + 2 \cdot 3 \cdot L_{\min} \right)$                                   | $\sqrt{\text{Area}_{\text{MOS}}} = 4.94 \mu\text{m}$ | MOS Area            |

| Area := $(Area_R + Area_{CAP} + Area_{BJT} + Area_{MOS})$                                                                                                       | $\sqrt{\text{Area}} = 14.5\mu\text{m}$               | Total Area          |

| Power Dissipation of Circuit                                                                                                                                    |                                                      |                     |

| $I_{VDD} := 2 \cdot I$                                                                                                                                          | $I_{VDD} = 147.22 \mu A$                             | Current from Supply |

| Power := $2 \cdot I \cdot V_{DD}$                                                                                                                               | Power = 0.44  mW                                     | Power Dissipation   |

| Cost of Circuit (Including Power)                                                                                                                               |                                                      |                     |

| $C_A := 5 \frac{\text{cents}}{C_P} = \frac{40 \text{cents}}{C_P}$                                                                                               |                                                      |                     |

## С

| $C_{\Lambda} := 5 \frac{\text{cents}}{1}$ | $C_{\rm p} := \frac{40 {\rm cents}}{1000}$        |

|-------------------------------------------|---------------------------------------------------|

| $C_{\rm A} = 3 \frac{1}{\rm mm^2}$        | $Cp = \frac{1}{2.7 \text{V} \cdot 200 \text{mA}}$ |

| 111111                                    |                                                   |

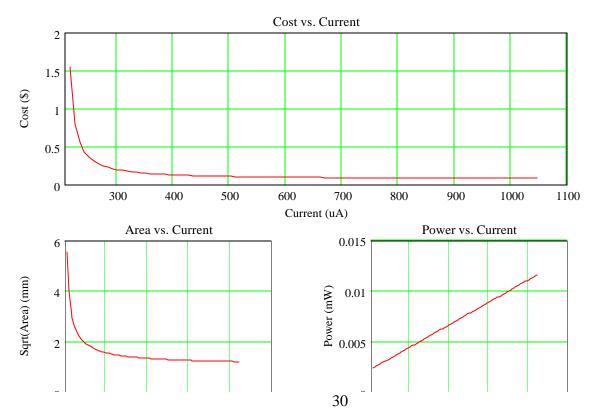

$Cost := C_A \cdot Area + C_P \cdot Power$

Ρ

Cost = 0.03 cents

One interesting point can be seen from the plot of the bandgap voltage with process variations is that the bandgap voltage varies more with process variations than it does with temperature. Care must be taken, when designing curvature correction circuits for bandgaps, to make sure the variations are not limited by random variations.

Fig. 1: Basic BiCMOS bandgap with device sizes and performance

OpAmp Vtol w/ NMOS Follower

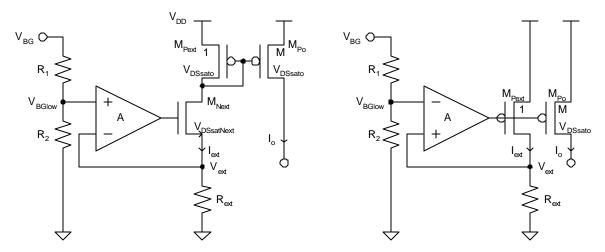

# **Option #1: Mirror Bandgap Current from Bandgap's Emitter Follower:**

Fig. 1: Bandgap Current Generator Circuit (Option #1)

There are several ways to generate a bandgap current. The easiest method is mirror off the bandgap current directly from collector of the emitter follower,  $Q_6$ , in the bandgap circuit. This method doesn't work for supply voltages below ( $V_{bg} + V_{CEsat} + V_{TPmax} + V_{DSsatmin}$ )=2.63V. Current technology requires a minimum supply voltage of 2.7V, which will be changing to 2.25V in the near future. To be safe, it is best to use another bandgap circuit, which will work with low power supplies.

| V <sub>DDmin</sub> | $option1 \coloneqq V_{bgm}$ | $ax + V_{CEsat} + V_{TP}$ | <sub>max</sub> + V | DSsatm | in   | V <sub>DDn</sub> | ninoptior | $_{11} = 2.$ | 73 V |   |      |   |   |   |

|--------------------|-----------------------------|---------------------------|--------------------|--------|------|------------------|-----------|--------------|------|---|------|---|---|---|

| TC 1               | 11                          | 11 A A A A A A            | 11 1               |        | ~~ · | • • •            |           |              | •    | • | a. • | c | 1 | • |

$Bandgap^I Design and Parages are available, it is usually best to maximize V_{DSsat}s to reduce noise. In this case for design an$ upper limit is set on V<sub>DSsat</sub>:

$V_{DSsatmax} := V_{DDmin} - (V_{bgmax} + V_{CEsat} + V_{TPmax})$

$V_{DSsatmax} = 0.17 V$

#### Variance in Output Current

Other than headroom a minor downfall of this option is the variance in the output current due to base current variation from the bandgap transistors.

$$I_{O} = \left(\frac{V_{bg}}{R_{ext}} + 2 \cdot I_{b}\right) M = \left(\frac{V_{bg}}{R_{ext}} + \frac{2 \cdot I}{\beta}\right) M = \left[\frac{V_{bg} \cdot \left(1 + \sigma_{\Delta V bg} - V bg\right)}{R_{ext} \cdot \left(1 + \sigma_{\Delta Rext} - Rext\right)} + \frac{2 \cdot I \cdot \left(1 + \sigma_{\Delta I} - I\right)}{\beta \cdot \left(1 + \sigma_{\Delta \beta} - \beta\right)}\right] M$$

The variance in the output current is calculated with the following substitutions:

$$I = I \cdot (1 + \sigma_{\Delta I\_I}) \quad \beta = \beta \cdot (1 + \sigma_{\Delta\beta\_\beta}) \quad R_{ext} = R_{ext} \cdot (1 + \sigma_{\Delta Rext\_Rext}) \quad V_{bg} = V_{bg} \cdot (1 + \sigma_{\Delta V bg\_V bg})$$

To yield the following equation:

$$\mathbf{I}_{o} + \sigma_{\Delta Io} = \frac{\mathbf{V}_{bg} \cdot \left(1 + \sigma_{\Delta V bg\_V bg}\right)}{\mathbf{R}_{ext} \cdot \left(1 + \sigma_{\Delta Rext\_Rext}\right)} + \frac{2 \cdot \mathbf{I} \cdot \left(1 + \sigma_{\Delta I\_I}\right)}{\beta \cdot \left(1 + \sigma_{\Delta \beta\_\beta}\right)}$$

This can be simplified to find the variance in the output current:

$$\sigma_{\Delta Io\_Io} = \frac{I_o - 2 \cdot I_b}{I_o} \cdot \left( \sigma_{\Delta Vbg\_Vbg} + \sigma_{\Delta Rext\_Rext} \right) + 2 \cdot \frac{I_b}{I_o} \cdot \left( \sigma_{\Delta I\_I} + \sigma_{\Delta \beta\_\beta} \right)$$

From this equation we can get insight into the sizing of I<sub>o</sub> (and thus R<sub>ext</sub>) to suppress variances in Beta.

#### Current Noise Calculations

It might be best to quantify the output noise in terms of a noise voltage so that options 1, 2 and 3 can be compared accurately. The noise voltage would be defined at noise at the output of the gate of the PMOS current mirror. Note that these noise derivation will put constraints on Rext and gmi in the op-amp section. The noise in the output current is:

$$\sigma_{\text{Ion}}^{2} = \left[ \left( \frac{V_{\text{bgn}}}{R_{\text{ext}}} \right)^{2} + 2 \cdot 2 \cdot q \cdot I_{\text{b}} + 4 \cdot k \cdot \text{Temp} \cdot \frac{1}{R_{\text{ext}}} \right] \cdot M^{2} + 4 \cdot k \cdot \text{Temp} \cdot \frac{2 \cdot 2 \cdot I_{\text{o}}}{3 \cdot V_{\text{DSsat}}} + 4 \cdot k \cdot \text{Temp} \cdot \frac{2 \cdot 2 \cdot I_{\text{o}}}{3 \cdot V_{\text{DSsat}}} \cdot M$$

We can use the following expression for the output current to solve for M.

$$I_0 = M \cdot \frac{V_{bg}}{R_{ext}}$$

$M = \frac{I_0 \cdot R_{ext}}{V_{bg}}$

At the same time we substitute in the expression for the base current I<sub>b</sub>.

$$I_b = \frac{V_{bg}}{\beta \cdot R_{ext}}$$

M is substituted into the bandgap expression to solve for R<sub>ext</sub>.

$$\sigma_{\text{Ion}}^{2} = \left[ \left( \frac{V_{\text{bgn}}}{R_{\text{ext}}} \right)^{2} + 2 \cdot 2 \cdot q \cdot \frac{V_{\text{bg}}}{\beta \cdot R_{\text{ext}}} + 4 \cdot k \cdot \text{Temp} \cdot \frac{1}{R_{\text{ext}}} \right] \cdot \left( \frac{I_{0} \cdot R_{\text{ext}}}{V_{\text{bg}}} \right)^{2} + 4 \cdot k \cdot \text{Temp} \cdot \frac{2 \cdot 2 \cdot I_{0}}{3 \cdot V_{\text{DSsat}}} + 4 \cdot k \cdot \text{Temp} \cdot \frac{2 \cdot 2 \cdot I_{0}}{3 \cdot V_{\text{DSsat}}} + \frac{1}{3 \cdot V_{\text{DSsat}}} \cdot \frac{I_{0} \cdot R_{\text{ext}}}{V_{\text{bg}}}$$

The noise from the last mirror transistor is subtracted off and the expression is simplified

$$\sigma_{\text{Ion}}^2 - 4 \cdot \text{k} \cdot \text{Temp} \cdot \frac{2 \cdot 2 \cdot I_0}{3 \cdot V_{\text{DSsat}}} = \frac{V_{\text{bgn}}^2}{V_{\text{bg}}^2} \cdot I_0^2 + \left(\frac{1}{V_{\text{T}}} \cdot \frac{1}{\beta} + \frac{1}{V_{\text{bg}}} + \frac{2 \cdot 2}{3 \cdot V_{\text{DSsat}}}\right) \cdot 4 \cdot \text{k} \cdot \text{Temp} \cdot I_0^2 \cdot \frac{R_{\text{ext}}}{V_{\text{bg}}}$$

We substitute in a quick approximation for the noise of the bandgap to help us budget the noise.

$$\sigma_{Vbgn}^2 = 4 \cdot k \cdot \text{Temp} \cdot K_{ptat}^2 \cdot \frac{V_T}{I}$$

bandgap quick approximation ( $K_{ptat}$  is on the order of 20)

Bandgap Design and Analysis Thus for the same current the bandgap contributes  $65\%(V_{DSsat}=200mV)-80\%(V_{DSsat}=1V)$  and the resistor about 10%, the base current about 5%, and the current mirror about 35%. The budgeting is a significant function of V<sub>DSsat</sub>, but we'll assume 75% for the bandgap and 25% for the other components, which are fixed by the resistor value.

$$\sigma_{\text{Ion}}^{2} - 4 \cdot k \cdot \text{Temp} \cdot \frac{2 \cdot 2 \cdot I_{0}}{3 \cdot \text{V}_{\text{DSsat}}} = 4 \cdot k \cdot \text{Temp} \cdot I_{0}^{2} \cdot \left[ \frac{\text{K}_{\text{ptat}}^{2} \cdot \text{V}_{\text{T}} \cdot 2}{\text{V}_{\text{bg}}^{2} \cdot \text{I}} + \left( \frac{1}{\text{V}_{\text{T}}} \cdot \frac{1}{\beta} + \frac{1}{\text{V}_{\text{bg}}} + \frac{2 \cdot 2}{3 \cdot \text{V}_{\text{DSsat}}} \right) \right]^{\frac{1}{1}}$$

$$\frac{\frac{\text{K}_{\text{ptat}}^{2} \cdot \text{V}_{\text{T}} \cdot 2}{\text{V}_{\text{bg}}^{2}}}{\left[ \frac{\text{K}_{\text{ptat}}^{2} \cdot \text{V}_{\text{T}} \cdot 2}{\text{V}_{\text{bg}}^{2}} + \left( \frac{1}{\text{V}_{\text{T}}} \cdot \frac{1}{\beta} + \frac{1}{\text{V}_{\text{bg}}} + \frac{2 \cdot 2}{3 \cdot \text{V}_{\text{DSsat}}} \right) \right]} = 89.06\% \text{ Bandgap}$$

$$\frac{\frac{\text{K}_{\text{ptat}}^{2} \cdot \text{V}_{\text{T}} \cdot 2}{\text{V}_{\text{bg}}^{2}} + \left( \frac{1}{\text{V}_{\text{T}}} \cdot \frac{1}{\beta} + \frac{1}{\text{V}_{\text{bg}}} + \frac{2 \cdot 2}{3 \cdot \text{V}_{\text{DSsat}}} \right) = 5.08\% \text{ Resistor}$$

$$\frac{\frac{1}{\text{V}_{\text{pg}}} \cdot \frac{1}{\text{V}_{\text{T}}} \cdot \frac{1}{\beta}}{\frac{1}{\text{V}_{\text{T}}} \cdot \frac{1}{\beta}} + \frac{1}{\frac{1}{\text{V}_{\text{bg}}}} + \frac{2 \cdot 2}{3 \cdot \text{V}_{\text{DSsat}}} \right) = 2.43\% \text{ Base}$$

$$\frac{\frac{1}{\text{K}_{\text{ptat}}^{2} \cdot \text{V}_{\text{T}} \cdot 2}{\text{V}_{\text{bg}}^{2}} + \left( \frac{1}{\text{V}_{\text{T}}} \cdot \frac{1}{\beta} + \frac{1}{\text{V}_{\text{bg}}} + \frac{2 \cdot 2}{3 \cdot \text{V}_{\text{DSsat}}} \right) = 3.43\% \text{ Current Mirror}$$

$$\frac{\frac{\text{K}_{\text{ptat}}^{2} \cdot \text{V}_{\text{T}} \cdot 2}{\text{V}_{\text{bg}}^{2}} + \left( \frac{1}{\text{V}_{\text{T}}} \cdot \frac{1}{\beta} + \frac{1}{\text{V}_{\text{bg}}} + \frac{2 \cdot 2}{3 \cdot \text{V}_{\text{DSsat}}} \right)$$

$$we can size the current-setting resistor$$

Now

$$R_{ext} := \frac{\left(\sigma_{Ion}^{2} - 4 \cdot k \cdot \text{Temp} \cdot \frac{2 \cdot 2 \cdot I_{o}}{3 \cdot V_{DSsat}}\right) \cdot 25\%}{\left(\frac{1}{V_{T}} \cdot \frac{1}{\beta} + \frac{1}{V_{bg}} + \frac{2 \cdot 2}{3 \cdot V_{DSsat}}\right) \cdot \frac{4 \cdot k \cdot \text{Temp} \cdot I_{o}^{2}}{V_{bg}}}{R_{ext}} = 311.23 \text{ k}\Omega$$

Now the value for M can be found

$$M := \frac{I_0 \cdot R_{ext}}{V_{bg}} \qquad M = 3.89$$

**Current Mirror Ratio**

OpAmp Vtol w/ NMOS Follower

CMOS Bandgap

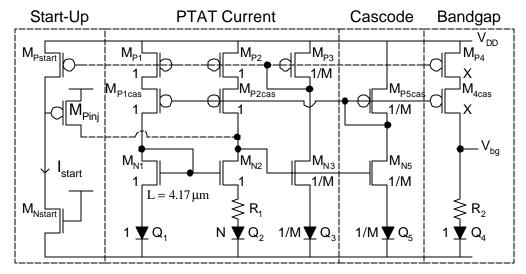

#### CMOS Bandgaps

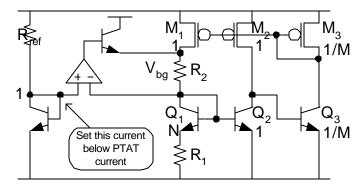

All bandgaps, including CMOS bandgaps, have the same basic structure: A PTAT current is generated and dropped across a resistor and diode. A common CMOS bandgap generator is shown in the following circuit. The main difference between a BiCMOS and CMOS PTAT current generator is the addition of a NMOS current mirror or operational amplifier to fix the voltage across the PTAT voltage. In the following figure, these MOS devices consist of MN1 and MN2. It is these two devices which greatly reduces the performance of a CMOS bandgap with respect it's BiCMOS counterpart. The mismatches and the noise in the NMOS devices are greatly amplified to the output. For a and untured handson a DiOMOC handson will arbitist unisticate lass than 10/ while it's OMOC counterment arbitist

Bandgap Design and Analysis variations in the 5% range.

A self-biased cascode CMOS bandgap with start-up circuit is shown in the following figure. The circuit looks complicated and like it will consume much current, because of the many bias legs. In reality the circuit only consumes a small increase increase in current from a regular bandgap, because most of the bias currents are smaller than the core bandgap current.

Fig. 1: CMOS bandgap and start-up circuit with low sensitivity to process variations and rout

The noise analysis, bandgap variation analysis, and device sizing routines are nearly identical to the circuit without cascodes. The cascode devices are sized identically to the PMOS current mirror devices, and the cascode bias generator is sized 1/4 the size the other PMOS devices.

The design procedure for CMOS bandgaps is similar to that of BiCMOS bandgaps:

- 1. Size V<sub>DSsat</sub>s for headroom constraints.

- 2. Size the current for thermal leaving a 3dB budget for 1/f noise.

- 3. Size the MOS lengths for 1/f noise

- 4. Size BJT area, resistor widths, and MOS lengths for matching.

- 5. Size MOS widths.

- 6. Size capacitors for stability if necessary

Thus we begin the design procedure by finding the headroom constraints.

CMOS Bandgap

CMOS BG Headroom Constraints

## **CMOS Bandgap Headroom Constraints**

The sizing of the CMOS bandgap begins with the DC biasing constraints. First we make the NMOS  $V_{DSsatN}$  as low as possible to minimize thermal and 1/f noise.

$V_{DSsatN} := 100 \text{mV}$

The PMOS cascodes are sized near minimum to maximum headroom.

$V_{DSsatPcas} := 0.15V$

The lengths of the PMOS cascodes are sized to a minimum to save area. This has negligible impact on 1/f noise and variation in the bandgap voltage.

$L_{Pcas} := L_{min}$

The bipolar transistor ratio, N, is sized a convenient ratio for layout: 3, 8, 24. Increasing N results in an exponential increase in area for a linear improvement in noise. A good compromise of area and power is an N of 8. Changing from N=8 to N=24 will increase the area by 300% for only a 33% reduction in power.

Ba N = 8 Design and Analysis

We make the current mirror ratios for the bias circuits just large enough to make the currents negligible. S = 5 M := 4

The PTAT current is mirrored to the bandgap increased by a factor of X. Increasing the factor X reduces the thermal noise, which indirectly allows current to be reduced, but directly increases the power dissipation. Decreasing X increases resistor area and decreased MOSFET area slightly. X can be optimized to save power, but here we choose a value of 1 for simplicity.

X = 1

The  $V_{DSsat}$ 's of the PMOS current mirror transistors are sized as large as possible under the worst case scenario, to minimize noise and improve matching for a given area.

V<sub>DSsatP1</sub> := V<sub>DDmin</sub> - V<sub>BEmax</sub> - V<sub>DSsatN</sub> - V<sub>TNmax</sub> - V<sub>DSsatPcas</sub> V<sub>DSsatP1</sub> = 0.85 V V<sub>DSsatP2</sub> := V<sub>DDmin</sub> - V<sub>BEmax</sub> - V<sub>DSsatN</sub> - V<sub>TPmax</sub> V<sub>DSsatP2</sub> = 0.9 V V<sub>DSsatP</sub> := min((V<sub>DSsatP1</sub> V<sub>DSsatP2</sub>)) The minimum supply voltage is found using minimum V<sub>DSsat</sub>s for the worst case bias leg. V<sub>DDbgmin1</sub> := V<sub>bgmax</sub> + V<sub>DSsatmin</sub> + V<sub>DSsatmin</sub> N<sub>DDbgmin1</sub> = 1.73 V V<sub>DDbgmin2</sub> := V<sub>TPmax</sub> + V<sub>DSsatmin</sub> + V<sub>DSsatmin</sub> + V<sub>DSsatmin</sub> + V<sub>BE</sub> V<sub>DDbgmin2</sub> = 2.3 V V<sub>DDbgmin3</sub> := V<sub>DSsatmin</sub> + V<sub>DSsatmin</sub> + V<sub>TNmax</sub> + V<sub>DSsatmin</sub> + V<sub>BE</sub> V<sub>DDbgmin3</sub> = 2.2 V V<sub>DDbgmin1</sub> := max((V<sub>DDbgmin1</sub> V<sub>DDbgmin2</sub> V<sub>DDbgmin3</sub>)) V<sub>DDbgmin</sub> = 2.3 V

Noise of Improved CMOS Bandgap

# Noise Analysis of CMOS Bandgap with Improved Sensitivity to Rout

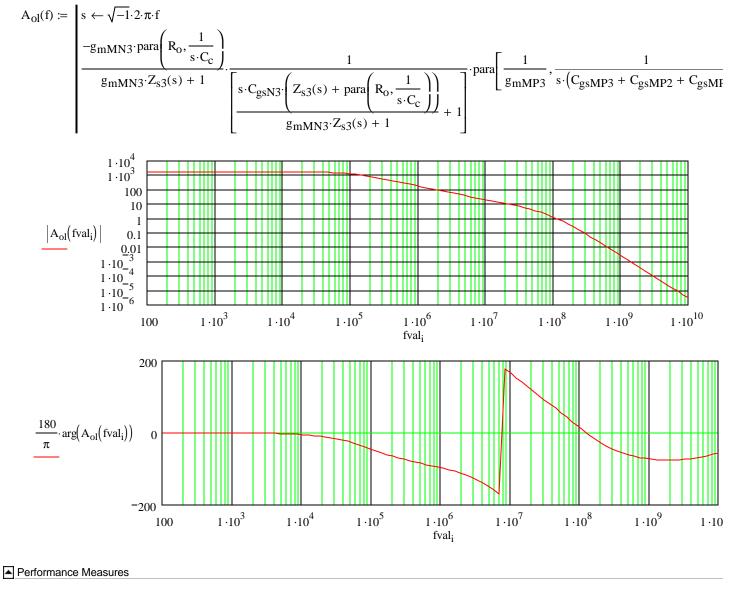

Once we know the headroom constraints, the required current is calculated to meet the noise constraints. This begins by performing a small signal analysis of the circuit. As with the BiCMOS bandgap there are four equations and four unknowns.

$$v_{1} = -g_{mMP1} \cdot (v_{2} + v_{nMP1}) \cdot \left(\frac{1}{g_{mMN1}} + \frac{1}{g_{mQ1}} + R_{1}\right) + v_{nMN1} + v_{nR1} + v_{nQ1}$$

$$v_{2} = -g_{mMN3} \cdot (v_{3} + v_{nMN3}) \cdot \frac{1}{g_{mMP3}} + v_{nMP3}$$

$$v_{3} = -\left[g_{mMP2} \cdot (v_{2} + v_{nMP2}) + \frac{g_{mMN2}}{1 + g_{mMN2} \cdot \frac{1}{g_{mQ2}}} \cdot (v_{1} + v_{nMN2} + v_{nQ2})\right] \cdot R_{0}$$

Simplify and solving for  $v_2$ , which will be used to solve for  $v_{hg}$ :

$$v_{2}^{2} = \frac{2}{\left(g_{mMP1} \cdot R_{1}\right)^{2}} \cdot v_{nMN1}^{2} + \left[\frac{\left(1 + \frac{g_{mQ1}}{g_{mMN1}}\right)^{2}}{\left(R_{1} \cdot g_{mQ1}\right)^{2}} + \frac{\left(R_{1} \cdot g_{mQ1} + \frac{g_{mQ1}}{g_{mMN1}} + 1\right)^{2}}{\left(R_{1} \cdot g_{mQ1}\right)^{2}}\right] \cdot v_{nMP1}^{2} + \frac{2 \cdot v_{nQ1}^{2}}{\left(g_{mMP1} \cdot R_{1}\right)^{2}} + \frac{v_{nR1}^{2}}{\left(g_{mMP1} \cdot R_{1}\right)^{2}}$$

This is simplified with the following variable substitutions:

$$g_{mQ1} = g_m = \frac{I}{V_T} v_{nQ1}^2 = v_{nQ2}^2 = 4 \cdot k \cdot \text{Temp} \cdot \frac{V_T}{2 \cdot I} \qquad v_{nR1}^2 = 4 \cdot k \cdot \text{Temp} \cdot \frac{V_T \cdot \ln(N)}{I}$$

Bandara Design and Analysis

$$R_{1} = \frac{V_{T} \cdot \ln(N)}{I} \qquad g_{mMN1} = \frac{2 \cdot I}{V_{DSsatN}} \qquad v_{nMN1}^{2} = 4 \cdot k \cdot \text{Temp} \cdot \frac{2}{3 \cdot \frac{2 \cdot I}{V_{DSsatN}}}$$

$$g_{mMP1} = \frac{2 \cdot I}{V_{DSsatP}} \qquad v_{nMP1}^{2} = 4 \cdot k \cdot \text{Temp} \cdot \frac{2}{3 \cdot \frac{2 \cdot I}{V_{DSsatN}}}$$

$$v_{2}^{2} = 4 \cdot k \cdot \text{Temp} \cdot \frac{V_{T}}{I \cdot \ln(N)^{2}} \left(\frac{V_{DSsatP}}{V_{T}}\right)^{2} \cdot \left[\frac{V_{DSsatN}}{6 \cdot V_{T}} + \left[\left(1 + \frac{V_{DSsatN}}{2 \cdot V_{T}}\right)^{2} + \left(\ln(N) + \frac{V_{DSsatN}}{2 \cdot V_{T}} + 1\right)^{2}\right] \cdot \frac{V_{T}}{3 \cdot V_{DSsatP}} + \frac{1 + \ln(N)}{4}$$

Now applying  $v_2^2$  to find the output noise:

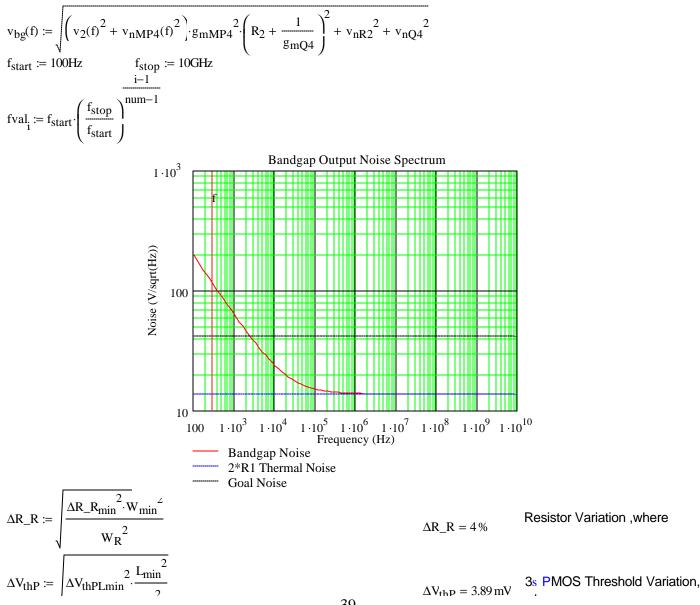

$$v_n^2 = (v_2^2 + v_{nMP4}^2) g_{mMP4}^2 \cdot (R_2 + \frac{1}{g_{mQ4}})^2 + v_{nR2}^2 + v_{nQ4}^2$$

Making the following variable substitutions:

$$\frac{R_2}{R_1} = \frac{K_{\text{ptat}}}{X \cdot \ln(N)} \qquad g_{\text{mMP4}} = \frac{2 \cdot I \cdot X}{V_{\text{DSsatP}}} \qquad v_{\text{nMP4}}^2 = 4 \cdot k \cdot \text{Temp} \cdot \frac{2}{3 \cdot \frac{2 \cdot I \cdot X}{V_{\text{DSsatP}}}}$$

$$v_{nR2}^{2} = 4 \cdot k \cdot \text{Temp} \cdot R_{2} \qquad v_{nQ4}^{2} = 4 \cdot k \cdot \text{Temp} \cdot \frac{V_{T}}{2 \cdot I \cdot X} \quad g_{mQ4} = \frac{I \cdot X}{V_{T}}$$

$$v_{bg}^{2} = 4 \cdot k \cdot \text{Temp} \cdot \frac{V_{T}}{v_{n}^{2}} \cdot \left[ \left[ \frac{2}{3} \cdot \frac{V_{DSsatN}}{V_{T}} + \left[ \left( 1 + \frac{V_{DSsatN}}{2 \cdot V_{T}} \right)^{2} + \left( \ln(N) + \frac{V_{DSsatN}}{2 \cdot V_{T}} + 1 \right)^{2} \right] \cdot \frac{4}{3} \cdot \left( \frac{V_{T}}{V_{DSsatP}} \right) \dots \right] \cdot \frac{1}{\ln(N)^{2}} \cdot \left( \frac{V_{T}}{V_{DSsatP}} \right)$$

Assuming  $V_{bg}$ - $V_{BE0}$ >> $V_T$ , the bandgap noise can be expressed as:

$$v_{bg}^{2} = 4 \cdot k \cdot \text{Temp} \cdot \frac{V_{T}}{v_{n}^{2}} \cdot \left[ \left[ \frac{2}{3} \cdot \frac{V_{DSsatN}}{V_{T}} + \left[ \left( 1 + \frac{V_{DSsatN}}{2 \cdot V_{T}} \right)^{2} + \left( \ln(N) + \frac{V_{DSsatN}}{2 \cdot V_{T}} + 1 \right)^{2} \right] \cdot \frac{4}{3} \cdot \left( \frac{V_{T}}{V_{DSsatP}} \right) \dots \right] \cdot \frac{1}{\ln(N)^{2}} \cdot K_{ptat}^{2} + \frac{K_{pta}}{X}$$

$$h \text{ bring for current } I$$

- V<sub>BE0</sub> VT

Solving for current, I

г

$$\mathbf{I} = 4 \cdot \mathbf{k} \cdot \text{Temp} \cdot \frac{\mathbf{V}_{\mathrm{T}}}{\mathbf{v}_{\mathrm{n}}^{2}} \cdot \left[ \left[ \frac{2}{3} \cdot \frac{\mathbf{V}_{\mathrm{DSsatN}}}{\mathbf{V}_{\mathrm{T}}} + \left[ \left( 1 + \frac{\mathbf{V}_{\mathrm{DSsatN}}}{2 \cdot \mathbf{V}_{\mathrm{T}}} \right)^{2} + \left( \ln(\mathbf{N}) + \frac{\mathbf{V}_{\mathrm{DSsatN}}}{2 \cdot \mathbf{V}_{\mathrm{T}}} + 1 \right)^{2} \right] \cdot \frac{4}{3} \cdot \left( \frac{\mathbf{V}_{\mathrm{T}}}{\mathbf{V}_{\mathrm{DSsatP}}} \right) \dots \right] \cdot \frac{1}{\ln(\mathbf{N})^{2}} \cdot \left( \mathbf{K}_{\mathrm{ptat}} + 1 \right)^{2} + \frac{\mathbf{K}_{\mathrm{ptat}}}{2 \cdot \mathbf{V}_{\mathrm{T}}} \right]$$

Repeating the noise derivation for 1/f noise alone we get

$$v_{bg1_{f}}^{2} = g_{mMP4}^{2} \cdot \left(R_{2} + \frac{1}{g_{mQ4}}\right)^{2} \cdot \left[v_{nMP4}^{2} + \frac{2 \cdot v_{nMN1}^{2}}{\left(g_{mMP1} \cdot R_{1}\right)^{2}} + \left[\frac{\left(1 + \frac{g_{mQ1}}{g_{mMN1}}\right)^{2}}{\left(R_{1} \cdot g_{mQ1}\right)^{2}} + \frac{\left(R_{1} \cdot g_{mQ1} + \frac{g_{mQ1}}{g_{mMN1}} + 1\right)^{2}}{\left(R_{1} \cdot g_{mQ1}\right)^{2}}\right] \cdot v_{nMP1}^{2}$$

-

Usually 1/f noise is dominated by NMOS transistors. Dropping the PMOS noise terms and substituting in expressions for the NMOS the bandgap noise becomes.

$$v_{nMN1}^2 = \frac{K_{fN}}{W \cdot L \cdot f}$$

$W_N = \frac{2 \cdot I \cdot L}{UNCOX \cdot V_{DS-VN}^2}$

$$\mathsf{Ba}_{v_{bg1_f}^2} = \left( \frac{\frac{\mathsf{v}_{DSsatP}}{\mathsf{ln}(N)} + \frac{\mathsf{v}_{DSsatP}}{\mathsf{V}_{T} \cdot \mathsf{ln}(N)}}{\mathsf{V}_{T} \cdot \mathsf{ln}(N)} \right) \cdot \frac{\mathsf{K}_{fN} \cdot \mu \mathsf{NCOX} \cdot \mathsf{V}_{DSsatN}^2}{\mathsf{I} \cdot \mathsf{L}_N^2 \cdot \mathsf{f}}$$

Here we see we can size L, given noise and current, or size current given noise and L. Increasing L saves current and increasing current saves area, but on the lower limit current is constrained by thermal noise. The required length to meet noise requirements are:

$$L_{N} = \left(\frac{K_{\text{ptat}}}{\ln(N)} + \frac{\frac{V_{\text{DSsatP}}}{2}}{V_{\text{T}} \cdot \ln(N)}\right) \cdot \frac{K_{\text{fN}} \cdot \mu \text{NCOX} \cdot V_{\text{DSsatN}}^{2}}{V_{\text{bg1}} \frac{2}{f} \cdot L_{\text{N}}^{2} \cdot f}$$

From this derivation of the bandgap noise, we see that for large  $R_{out}$  the noise of the this bandgap is exactly the same as a simpler bandgap, where the PMOS current is simply mirrored instead of being passed through a high-gain circuit. A simplified formula to quickly estimating bandgap noise from a given current is given below:

$$v_n^2 = 4 \cdot k \cdot \text{Temp} \cdot R_2 \cdot \frac{R_2}{R_1} = 4 \cdot k \cdot \text{Temp} \cdot \frac{V_T \cdot \ln(N)}{I} \cdot 20^2$$

Noise of Improved CMOS Bandgap

CMOS Bandgap Area

## CMOS Bandgap Area

Equations for the area of the CMOS bandgap and start-up circuits are important for optimization. The area takes the following form:

$$Area = 2 \cdot W_N \cdot \left(L_N + 2 \cdot L_{min}\right) + \left(2 + X + \frac{1}{M} + \frac{1}{S}\right) \cdot W_P \cdot \left(L_P + 2 \cdot L_{min}\right) + (N+1) \cdot Area \cdot Q_1 + W_R \cdot \left(L_{R1} + L_{R2} + L_{min}\right) \dots + \left(L_{start} + 2 \cdot L_{min}\right) \cdot W_{start}$$

If the circuit is cascoded the area becomes:

$$Area = 2 \cdot W_{N} \cdot \left(L_{N} + 2 \cdot L_{min}\right) + \left(2 + X + \frac{1}{M} + \frac{1}{S}\right) \left[W_{P} \cdot \left(L_{P} + 2 \cdot L_{min}\right) + W_{Pcas} \cdot \left(L_{Pcas} + 2 \cdot L_{min}\right)\right] + (N + 1) \cdot Area \cdot Q_{1} \dots + W_{R} \cdot \left(\frac{W_{R}}{R_{sq}} \cdot \frac{V_{T} \cdot \ln(N)}{I} + \frac{W_{R}}{R_{sq}} \cdot \frac{R_{2}}{R_{1}} \cdot \frac{V_{T} \cdot \ln(N)}{I} + L_{min}\right) + \left(L_{start} + 2 \cdot L_{min}\right) \cdot W_{start}$$

Making variable substitutions and simplifying to only active area

$$W_{N} = \frac{2 \cdot I \cdot L_{N}}{\mu N \text{COX} \cdot V_{\text{DSsatN}}^{2}} \qquad W_{P} = \frac{2 \cdot I \cdot L_{P}}{\mu N \text{COX} \cdot V_{\text{DSsatP}}^{2}} \qquad W_{\text{Pcas}} = \frac{2 \cdot I \cdot L_{\text{Pcas}}}{\mu N \text{COX} \cdot V_{\text{DSsatPcas}}^{2}} \qquad L_{R1} = \frac{W_{R}}{R_{\text{sq}}} \cdot R_{1} = \frac{W_{R}}{R_{\text{sq}}} \cdot \frac{V_{T} \cdot \ln(N)}{I}$$

$$L_{R2} = \frac{W_{R}}{R_{\text{sq}}} \cdot R_{2} = \frac{W_{R}}{R_{\text{sq}}} \cdot \frac{R_{2}}{R_{1}} \cdot \frac{V_{T} \cdot \ln(N)}{I}$$

The area becomes

$$Area = 2 \cdot \frac{2 \cdot I \cdot L_{N}^{2}}{\mu N \text{COX} \cdot V_{\text{DSsatN}}^{2}} + \left(2 + X + \frac{1}{M} + \frac{1}{S}\right) \left(\frac{2 \cdot L_{P}^{2}}{\mu N \text{COX} \cdot V_{\text{DSsatP}}^{2}} + \frac{2 \cdot L_{\text{Pcas}}^{2}}{\mu N \text{COX} \cdot V_{\text{DSsatPcas}}^{2}}\right) \cdot I + (N + 1) \cdot \text{Area} \cdot Q_{1} \dots$$

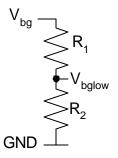

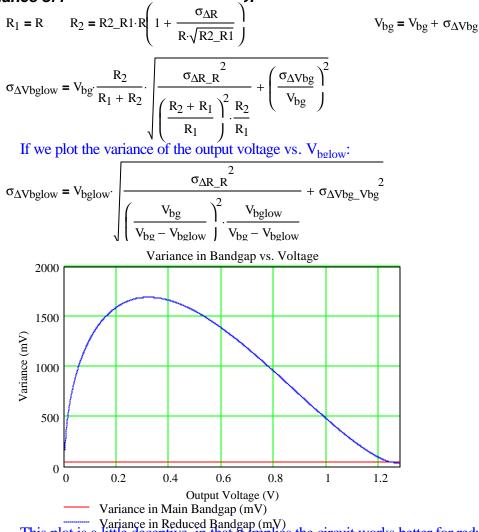

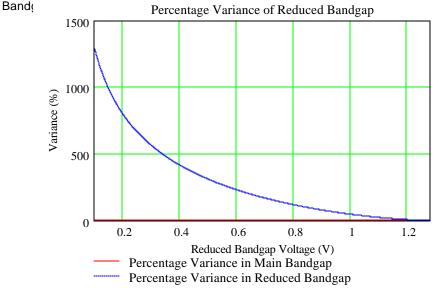

CMOS Bandgap Area